大家好、

在大规模生产中长时间使用 MSP430F67751A 系列微控制器。 但在某些产品中、我们开始看到特定的 DMA 传输问题。

我们使用一种算法、其中"Timer1 A1 Interrupt"触发10位 ADC 通道的自动扫描、自动扫描4个不同通道、然后触发 DMA 操作。 问题是、我们开始在某些产品的读数中看到"0"值。 为 ADC 操作添加条件语句时忽略"0"值,最终导致 UART 和 I2C 通道中缺少数据。 在 UART 外设中、我们使用轮询方法、如果知道的话。 此外、如果我们开始使用"Timer3 A1中断"、这是我们软件中开始增加并行处理器负载的关键点。

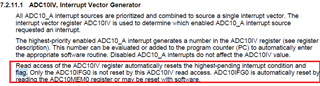

检查勘误表(请参阅 :https://www.ti.com/lit/er/slaz590v/slaz590v.pdf)、了解我们遇到的与"DMA7"代码相关的特定问题。 勘误表指出 DMA 传输可能会导致中断丢失。 但为什么我们的所有产品都没有发生这种情况。 由于我们在"Timer1 A1中断"末尾调用 ADC 扫描、因此如果我们不对该特定外设进行读写操作、DMA 操作可能会导致中断丢失。 此外、在读取时如何设置 DMA 和 ADC 外设的所有成功标志也是完全错误的。 我们还使用示波器检查了输入信号、没有看到尖峰或在其处切断。

谢谢、此致。