请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:MSP432P401R 当我读取 Comp_e_interrupt_output_toggle_Vref12V.c 的 msp432演示代码时

compConfig 为

const COMP_E_Config compConfig = { Comp_E_VREF、 //正输入端子 COMP_E_INPUT6、 //负输入端子 COMP_E_FILTEROUTPUT_DLYLVL4、//延迟级别4滤波器 COMP_E_NORMALOUTPUTPOLARITY //正常输出极性 };

当它进入 MAP_COMP_E_initModule 时、代码注释为

/*初始化比较器模块 *比较器实例1 *将 CE16引脚连接到正极(+)端子 *负(-)端子的基准电压 *正常功率模式 *输出滤波器开启且具有最大延迟 *同相输出极性 * MAP_COMP_E_initModule (COMP_E1_base、&compConfig);

正极和负极与配置进行比较。为什么?

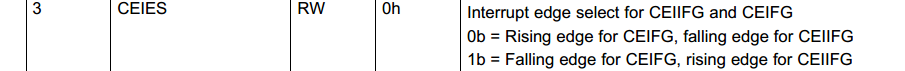

我查找它所说的 TRM

CEIES = 0是 Ring 边沿、CEIES = 1是下降边沿、但当它进入 driverLib 代码时

void COMP_E_setInterruptEdgeDirection (uint32_t 比较器、 uint_fast8_t 可得指令) { assert (edgeDirection <= COMP_E_RISINGEDGE); //设置将触发中断的边沿方向 IF (COMP_E_RISINGEDGE ==可生成方向) BITBAND_PERI (COMP_E_CMSIS (比较器)->CTL1、COMP_E_CTL1_IES_OFS)= 1; 否则、如果(COMP_E_FALINGEDGE =edgeDirection) BITBAND_peri (COMP_E_CMSIS (比较器)->CTL1、COMP_E_CTL1_IES_OFS)= 0; }

CEIES = 1是上升沿、CEIES = 0是下降沿?

我弄错了还是代码错误?