请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:MSP430F6775 您好、香榭丽舍

我的一位客户正在使用 F6775开发 MSP430应用。

最近、他们在掉电->开测试时成功解决了锁定问题。

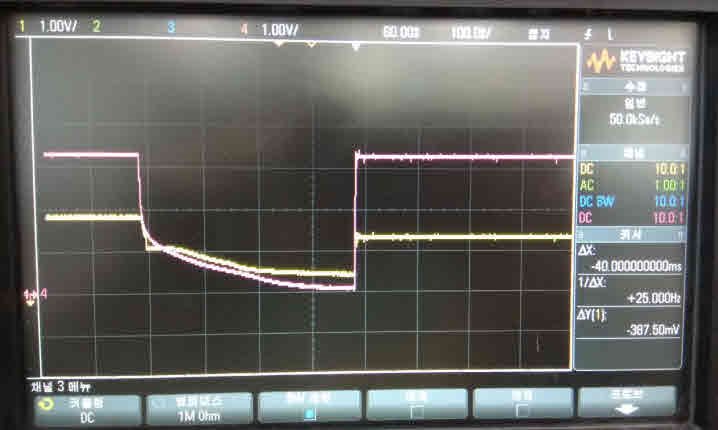

当在断电状态下降低电压电平时、其系统显示 Vcore 高于 DVCC、如下图所示。

如果它们在 Vcore > DVCC 和 DVCC > 1.4V 时通电、则 MCU 无法正常工作。

您知道原因吗?

请注意、如果它们将 C_Vcore 从470nF 更改为22nF、则它不能是 Vcore > DVCC 条件、那么它作为正常复位工作。

也请 参阅原理图以供参考。

此致、

欧内斯特