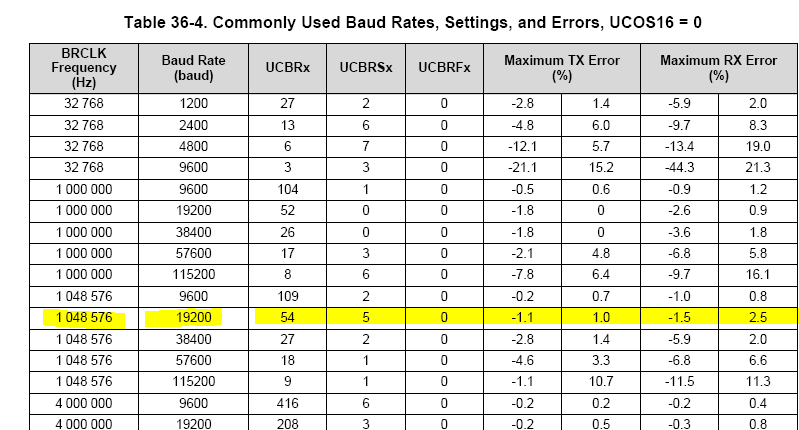

我将 MSP430f5310器件上的 Modbus 波特率从4800更改为19200、并看到一些高于预期的 TX 误差-当计时器设置的最大 TX 误差预计为4.6%时、大约为9.5%、如下面的表36-5所示。

这可能是器件的限制吗? 我可以做些什么来克服这种高误差率? 我是否可以通过测量来更准确地诊断我的问题?

辅助信息:我成功 地将器件设置为4800波特、而没有任何发送 或接收错误。 我在相对无噪声的环境中工作。 我正在使用 Code Composer Studio 编译 C 代码。 突出显示 的区域表示我为提高波特率所做的更改。

请提供建议。