Thread 中讨论的其他器件: CCStudio

您好!

我使用 MSP430F5172在具有 CCR1和 CCR2的计时器 D0上创建交错 PWM。 D0分别在增/减模式下运行、CCR1/2分别在比较模式切换复位和切换设置下运行。

PWM 正被正确交错;然而、当定时器同时启动两个输出高电平时、第一个脉冲上会出现问题、这是我们尝试避免的情况。

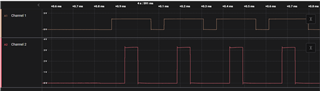

下面是信号的图像、其中 D0.1是 TD0 CCR1、D0.2是 TD0 CCR2。

在 TI 的 CCStudio 示例代码教程中分析这些信号时、也会发生这种现象。 是否有办法解决这个问题? 是否存在潜在的配置问题?

TI 的文档指出、此 PWM 设置非常适合两个信号不应同时处于高电平的情况、但这种启动行为无法实现目标... 这使我认为我有配置问题。

下面是设置代码。

void init_timers(void)

{

struct s_TLV_Timer_D_Cal_Data * pTD0CAL; // Structure initialized in tlv.h

uint8_t bTD0CAL_bytes;

// Stop WDT

WDT_A_hold(WDT_A_BASE);

//Get TimerD0 Cal Values (instance 0)

TLV_getInfo(TLV_TAG_TIMER_D_CAL, 0, &bTD0CAL_bytes, (uint16_t **) &pTD0CAL);

if(bTD0CAL_bytes == 0x0)

{

// No TimerD free running cal data found

while(1); // Loop here

}

/*

* Configuration

*/

// Setup TD0

TD0CTL0 |= TDCLGRP_0 | CNTL_0 | TDSSEL_2 | MC__UPDOWN | ID_0 | TDCLR;

TD0CTL1 |= TDIDEX_0 | TDCLKM_1;

// Enable high resolution clock

TD0HCTL0 = TDHEN + TDHM_1;

TD0HCTL1 = pTD0CAL->TDH0CTL1_128;

// Configure CCR modes

TD0CCTL0 |= TIMER_D_OUTPUTMODE_OUTBITVALUE;

TD0CCTL1 |= TIMER_D_OUTPUTMODE_TOGGLE_RESET;

TD0CCTL2 |= TIMER_D_OUTPUTMODE_TOGGLE_SET;

// Configure latching compare thresholds

...

}

感谢你的任何帮助。