Other Parts Discussed in Thread: MSP430F2132

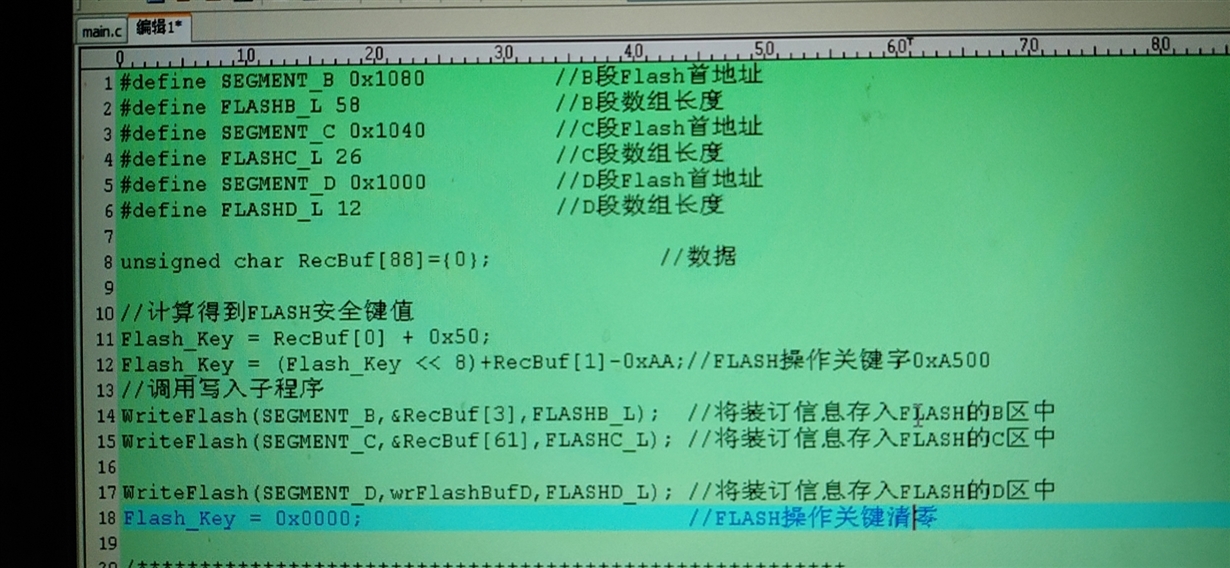

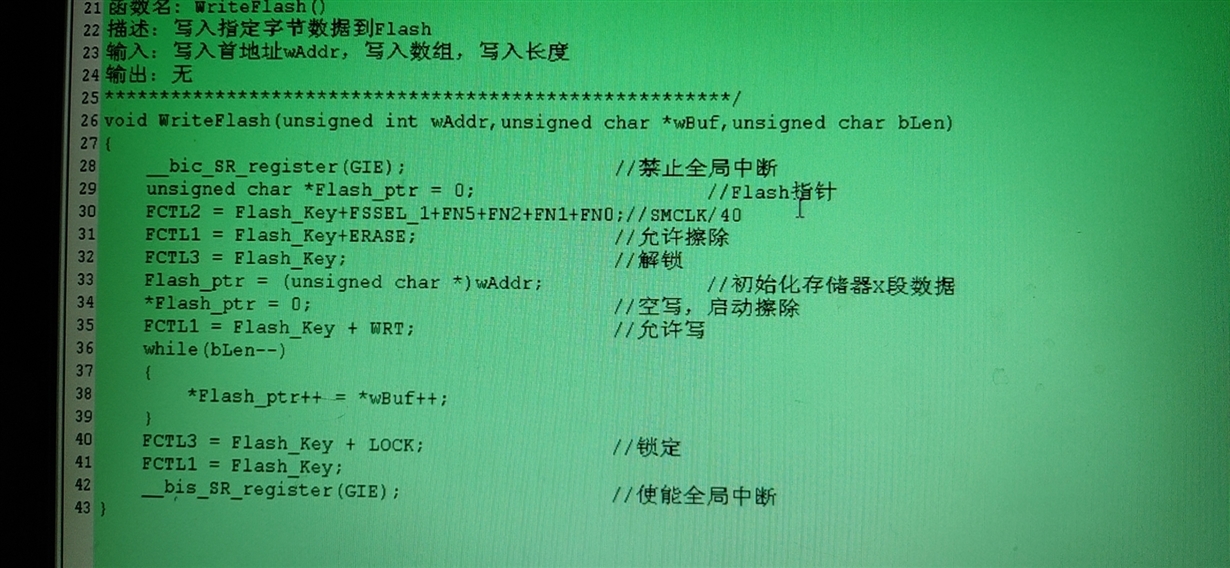

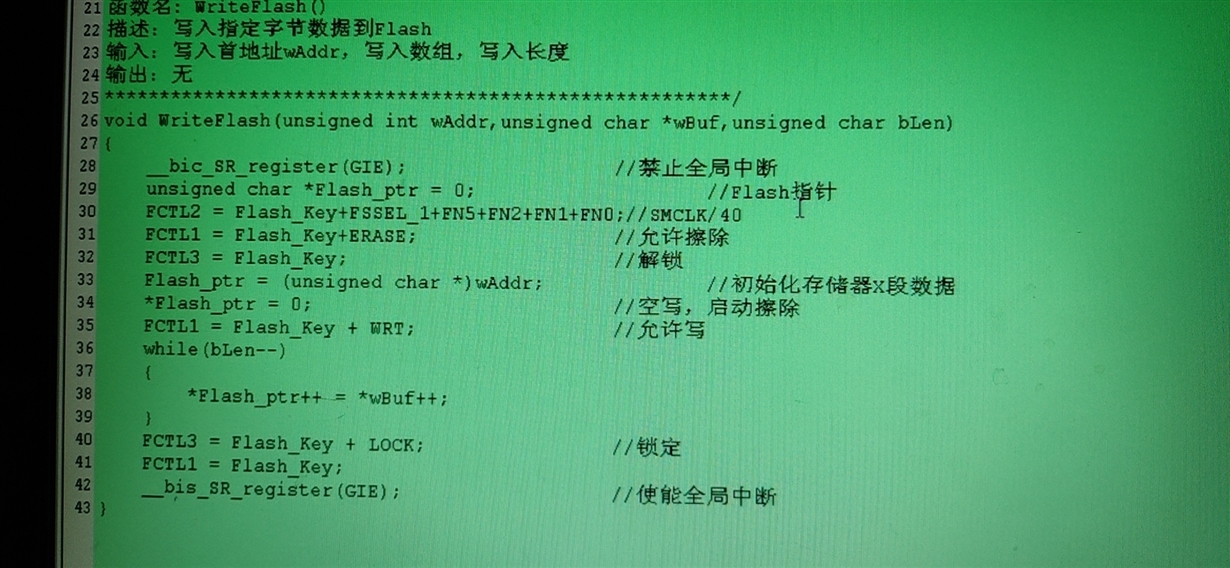

我们有一个项目将 TI MSP430F2132设计为产品控制器、将产品信息存储在芯片的闪存信息存储区的 B 和 C 段中。

在进行特定测试之后,一切正常,两天后产品重新通电,发现区域 B 和 C 中的数据更改为 FF (初始闪存状态)。 在这两项测试中、仅对产品执行了电气性能测试。 但是、只有闪存的 D 区域在电气性能中被读取和写入、并且在 B 和 C 区域中没有读取或写入操作。 我们想了解这种现象的可能原因。

备注:出现问题后、我们测试闪存 B 和 C 区的读写功能、芯片仍然可以正常使用。

我公司某项目应用了TI公司的MSP430F2132作为产品控制器,在其片内FLASH的信息存储器B段、C段存储了产品信息。μ A

某次测试正常后,隔两天对该产品再次上电测试,发现B区、C区数据均变为FF(flash初始状态),在两次测试期间,对该产品做过一次电性能测试,但是只对FLASH的D区进行过读写操作,B区、C区无读写操作。咨询一下产生该现象可能的原因。μ A

注:出现该问题后,对该产品FLASH的B区、C区进行读写测试,可以正常使用 μ A