主题中讨论的其他器件:EVM430-FR6043

社区您好。

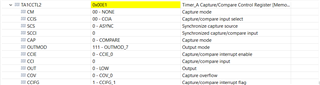

我使用 EVM430-FR6043板通过 Timer_A1模块创建 PWM。

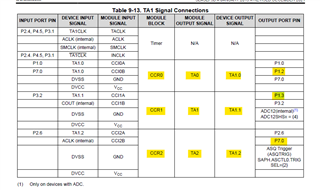

Timer_A1模块具有 TA1.0、TA1.1和 TA1.2引脚。

用于 TA1.0的 P1.2、用于 TA1.1的 P1.3以及用于 TA1.2的 P7.0

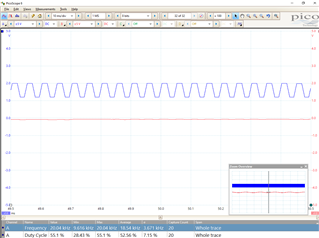

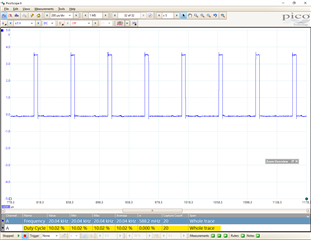

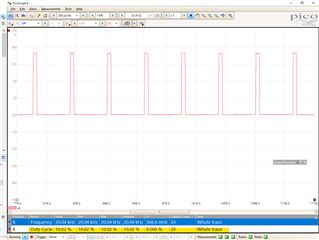

我读取示例代码以使用 Timer_A1生成两个 PWM、但无法生成正确的 PWM。

仅在 TA1.1 (P1.3)中发生 PWM 生成、占空比不正确。 我将提供占空比值、但创建的占空比值不同。

我附上了我的代码供您参考。 请帮助我解决此问题。

#include <msp430.h>

#include "timer_a.h"

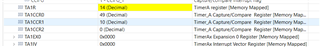

#define TIMER_PERIOD 49

#define DUTY_CYCLE1 5

#define DUTY_CYCLE2 5

Timer_A_initCompareModeParam pwm_gen_0;

Timer_A_initCompareModeParam pwm_gen_1;

Timer_A_initUpModeParam pwm_up;

/**

* main.c

*/

int main(void)

{

WDTCTL = WDTPW | WDTHOLD; // Stop WDT

// Configure GPIO

P1DIR |= BIT2; // P1.2 as output

P1DIR |= BIT3; // P1.3 as output

P7DIR |= BIT0; // P7.0 as output

P1SEL1 |= BIT2; // P1.2,P1.3 and P7.0 options select

P1SEL1 |= BIT3;

P7SEL1 |= BIT0;

// Disable the GPIO power-on default high-impedance mode to activate

// previously configured port settings

PM5CTL0 &= ~LOCKLPM5;

CSCTL0_H = CSKEY_H; // Unlock CS registers

CSCTL1 = DCOFSEL_6; // Set DCO = 8MHz

CSCTL2 = SELA__VLOCLK | SELS__DCOCLK | SELM__DCOCLK;// Set ACLK=VLO SMCLK=DCO

CSCTL3 = DIVA__8 | DIVS__8 | DIVM__8; // Set all dividers

CSCTL0_H = 0;

/*------- Timer A1------------*/

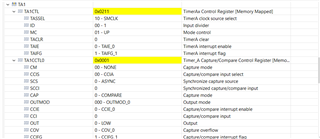

pwm_up.clockSource=TIMER_A_CLOCKSOURCE_SMCLK;

pwm_up.clockSourceDivider=TIMER_A_CLOCKSOURCE_DIVIDER_1;

pwm_up.timerPeriod=TIMER_PERIOD;

pwm_up.timerInterruptEnable_TAIE=TIMER_A_TAIE_INTERRUPT_DISABLE;

pwm_up.captureCompareInterruptEnable_CCR0_CCIE=TIMER_A_CCIE_CCR0_INTERRUPT_DISABLE;

pwm_up.timerClear=TIMER_A_DO_CLEAR;

pwm_up.startTimer=false;

pwm_gen_0.compareRegister=TIMER_A_CAPTURECOMPARE_REGISTER_1;

pwm_gen_0.compareInterruptEnable=TIMER_A_CAPTURECOMPARE_INTERRUPT_DISABLE;

pwm_gen_0.compareOutputMode=TIMER_A_OUTPUTMODE_RESET_SET;

pwm_gen_0.compareValue=DUTY_CYCLE1;

pwm_gen_1.compareRegister=TIMER_A_CAPTURECOMPARE_REGISTER_2;

pwm_gen_1.compareInterruptEnable=TIMER_A_CAPTURECOMPARE_INTERRUPT_DISABLE;

pwm_gen_1.compareOutputMode=TIMER_A_OUTPUTMODE_RESET_SET;

pwm_gen_1.compareValue=DUTY_CYCLE2;

Timer_A_initUpMode(TA1_BASE,&pwm_up);

Timer_A_initCompareMode(TA1_BASE,&pwm_gen_0);

Timer_A_initCompareMode(TA1_BASE,&pwm_gen_1);

Timer_A_startCounter(TA1_BASE,TIMER_A_UP_MODE);

return 0;

}

提前感谢、

萨尔沃特