我目前正在调试一个电流消耗问题、即 MSP430FR2111设置要在 P2.7/TB0CLK/XIN 引脚上使用外部32kHz 信号 。 在此模式下、该引脚上的接地阻抗是多少? 如果使用传统的皮尔斯振荡器、我认为典型的实现方案是一些从 XTAL 引脚接地的偏置电阻器。 我无法从文档中明确了解在该引脚上使用外部时钟源时是否完全旁路了 XOSC 的模拟部分。 根据总电流、它看起来像是 P2.7/TB0CLK/XIN 引脚贡献了一些额外的 uA、我正在尝试确定是否是这样。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

我目前正在调试一个电流消耗问题、即 MSP430FR2111设置要在 P2.7/TB0CLK/XIN 引脚上使用外部32kHz 信号 。 在此模式下、该引脚上的接地阻抗是多少? 如果使用传统的皮尔斯振荡器、我认为典型的实现方案是一些从 XTAL 引脚接地的偏置电阻器。 我无法从文档中明确了解在该引脚上使用外部时钟源时是否完全旁路了 XOSC 的模拟部分。 根据总电流、它看起来像是 P2.7/TB0CLK/XIN 引脚贡献了一些额外的 uA、我正在尝试确定是否是这样。

尊敬的 TheGhostOf:

我喜欢这个名字。

有关32KHz 振荡器的唯一文档将位于系列用户指南中。 我同意在旁路模式下还不清楚仍然连接到 XIN 引脚的是什么。 是否计划从外部时钟源驱动此引脚?

您需要测量多大的电流、目标是什么? 低于1uA?

您是否确定已正确配置 XT1引脚6、7、所有未使用的 IO 引脚均设置为输出并被驱动为低电平?

根据数据表第8.7节、室温下的典型电流为~1uA

- P2.7/TB0CLK/XIN 由一个带有32 kHz xtal 振荡器的芯片驱动,该振荡器可以在数字 IO 上输出32 kHz 时钟。

-我们在为 MSP 供电的电源上有一个磁珠,当替换为一个电阻器以测量 MSP 的电流消耗时,只有电流是预期的。

-在时钟驱动器侧做同样的操作,我看到电流比它应该高~8 -10 uA。 将 MSP 从系统中物理上移除、电流会回落到预期水平。

到目前为止、我所做的所有测试均表明 MSP 与提供32kHz 信号的芯片之间的接口。 我还切断了接口中的大部分线路、只留下32kHz 时钟线作为额外电流的原因。 我可以通过使用 xtal 为 MSP 计时来间接证明这一点(如果我找到一个) 但要知道如何在不增加成本的情况下解决这个问题、了解 P2.7/TB0CLK/XIN 在该模式下是否行为类似于数字引脚、或者时钟信号是否实际上馈送到 xtal 振荡器模块的输入将非常有帮助。 这是一种相当典型的实现方式、因为它节省了大量的内部逻辑(您链接的示例说明了这一点)。 您是否能够在内部与研发人员进行核实以进行验证?

连接到 P2.7的外部32kHz xtal 振荡器的最大输出电压是多少 VDD?

所有器件均采用3.3V 电源供电(32kHz 时钟的最大电压为3.3V)。 我没有发现任何可能导致域之间泄漏的东西等。

我必须检查代码。

但是:如果我在 MSP 上测量流入 VDD 的电流、这正如预期的那样。

仅5个引脚连接到电路的不同部分:

- P2.7 (32 kHz in )

-测试

- RST_N

-接收器(UART)

-发送器(UART)

我断开了 RX/TX、但未产生任何影响。

我现在还尝试使用 xtal 运行 MSP 并截断32k clk 线。 然后电流会以1uA 下降、而不是像我希望的那样以10uA 下降。

过量电流非常稳定、这意味着使用悬空引脚时不太可能发生这种情况。

我推断出这额外的10或12uA 归因于1.5Vref、因为当您禁用比较器和 DAC 时、电流会下降。

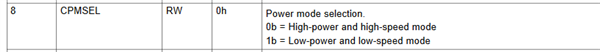

有一个针对比较器和 DAC 的静态流耗的技术规格。 DAC 电流可以忽略不计、但根据为比较器选择的功率模式、您可以看到高达22uA (典型值)、但我在您的代码中看到、您曾使用 CPMSEL = 1。

因此、展望未来、只要启用比较器或 DAC、您就可以预期会看到额外的电流、以便进行相应的规划。

我必须检查我们在代码中使用的是什么。 由于以下原因而启用 DAC:

CPDACCTL = CPDACEN | CPDACBUUFS

意味着 CPDACREFS = 0且 VDD 用作参考。

当我阅读用户指南时、1.5V 内部基准在不使用时应该被关闭、并且在这种情况下不应该对电流产生任何影响?

--

此外、我们在测试代码中关闭比较器、但仍启用 DAC、得出的差值电流为1.5uA、与数据表中的 ICOMP = 1.3uA 一致。 基本上指向与 MSP 的 DAC 部分相关的东西。

好的、好像内部 VREF (PMMCTL2 |= INTREFEN)启用时、我看到大约70uA。

如果我禁用内部 VREF、但将 DAC 配置为使用 VREF、我看到的是3.9uA。

如果我随后将 DAC 切换为改用 VDD、则测量值为13.7uA。 这告诉我、可能有一些内部分压器会将 DAC 基准的电压从3.3降至约1.5伏特。 这个分压器可能会消耗额外的10uA 电流。

谢谢你。

如果我禁用内部 VREF,但将 DAC 配置为使用 VREF,我看到的是3.9uA。

在这种情况下、DAC 是否有基准? 当我阅读用户指南时、这是一个简单的电阻式 DAC、这意味着在这种情况下输入未定义?

您是否知道数据表为什么不涵盖额外的~13uA? 数据表是2016年发布的、因此我有点惊讶、因为它缺少有关该电流的信息、因为它可能会 对低功耗应用产生重大影响。