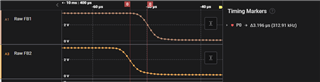

如标题所述、我将使用 P1.1和 P1.2来触发端口1中断服务例程、在下降沿触发。 请参见传入波形下降沿的屏幕截图。

在本例中、它们之间的间隔大约为3微秒。 当它们之间的间隔在~5微秒内时、无论哪一秒出现、似乎都不会发出它的标志。

端口1设置:

P1DIR &= ~(2 + 4); //Set P1.1 & P1.2 to Input P1IES |= (2 + 4); //Interrupt Edge Selection - high to low (1->0) P1IE |= (2 + 4); //P1.1 & P1.2 Interrupt Enable P1IFG &= ~(2 + 4); //Clear Interrupt Flags

端口1 ISR

#if defined(__TI_COMPILER_VERSION__) || defined(__IAR_SYSTEMS_ICC__)

#pragma vector=PORT1_VECTOR

__interrupt void Port_1(void)

#elif defined(__GNUC__)

void __attribute__ ((interrupt(PORT1_VECTOR))) Port_1 (void)

#else

#error Compiler not supported!

#endif

{

switch(P1IFG) {

case 2: //P1.1

doStuff();

P1IFG &= ~(BIT1); //Clear IFG P1.1

break;

case 4: //P1.2

doStuff();

P1IFG &= ~(BIT2); //Clear IFG P1.2

break;

case 6: //BOTH P1.1, P1.2

doStuff();

P1IFG &= ~(BIT1+BIT2); //Clear IFG P1.1 and P1.2

break;

default:

//do nothing

}

我对 MSP430中断架构的理解是、如果 P1IFG 中的另一位在 ISR 期间被提出、在 ISR 完成后、它应该立即重复其自身来处理下一个提出的标志。

g2553需要手动降低标志、因此它不是冗余的。

我之所以忽略它的理论是在"P1IFG &=~(BIT1)"的"读取、修改、写入"操作期间;此标志会在寄存器读入存储器后出现、这样、当修改后的数字被重新放入寄存器时、自升高后的标志会意外被清除。

我对这个理论有问题,但我目前没有更好的解释。

第二个中断标志未被发出有什么原因吗? 是不是有些后端架构问题?