我正在使用 该器件的看门狗计时器和 ACLK (看门狗的标准 WDT_ADLY_1000配置以提供1秒的中断)进行简单的计时、但我注意到 与确切 时间有很大偏差(每天最多3分钟)。

最初我在 XIN XOUT 上用的是32.768kHz 晶振、我换了另一个晶振、有负载电容、但仍然有这个重要的偏差、把这个故障放在了晶振上、买了一个25ppm 的参考时钟。 因此、现在我使用该时钟(3.3V、理想值为32768Hz)输入 XIN、但我仍然观察到相同的时间偏差。

经过深入研究、我发现 ACLK 输出与 XIN 信号无关;换句话说、无论我做什么、REF0CLK 信号都被用作 ACLK。

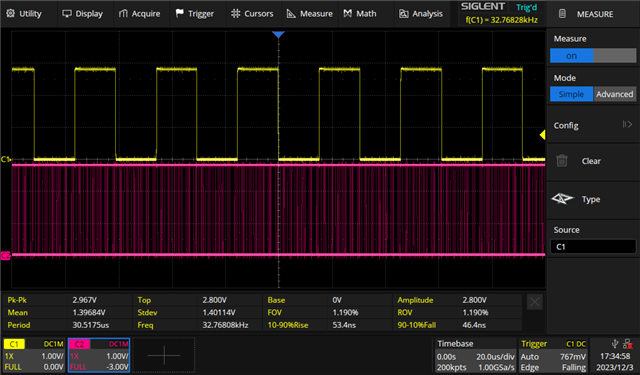

我附上了两个示波器屏幕截图、第一个在 XIN 输入上同步、第二个在 ACLK 输出上同步。

当然、我将 USCTL4配置为0 SELA 以选择 XT1 CLK、并将 USCTL6配置为 XT1BYPASS、并使用调试器确认了这些设置。

所以,在这一点上,我不知道什么可能是错的,任何帮助将会 非常感激!

XIN 信号(黄色) ACLK (粉色)、XIN 为32768Hz

长

相同、但在 ACLK 上同步、ACLK 的频率为32679Hz