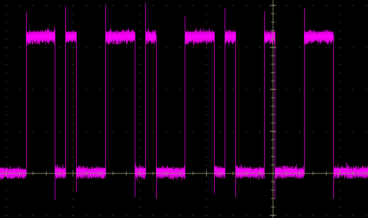

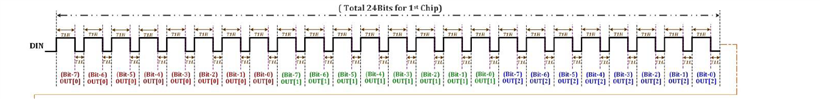

我使用的是 MSP430F6777A 微控制器。 SMCLK 的频率为25MHz。 我想切换 GPIO 引脚以驱动装配 LED。 对于此操作、我需要将 GPIO 引脚保持在高电平900ns、保持在低电平300ns。 循环和&&逻辑运算符的 IF 控制等操作会增加切换时间。 如何在不使用 PWM 模式下的计时器的情况下加快切换过程?

e2e.ti.com/.../AN1001_5F00_IC-Embedded-Solutions-of-SMD-LEDs-_2800_Ver-1.0_2900_.pdf

Toh=300ns

T0L=.00

T1H=.00

T1L= 300ns