您好!

我正在尝试同时运行两个计时器:用于生成 PWM 的 TimerA 和 TimerB。

定时器 A: 时钟源是使用16MHz 外部晶振的 TACLK (由另一个安装了 Y1的 msp430fr5969的引脚3.4提供16 MHz)

定时器 B:时钟源为 SMCLK、该时钟源映射到16MHz 的 MCLK (DCO 源)

我的最终目标是以高波特率生成2FSK 信号、为此、我将使用计时器 A 作为我的波特率源、并使用计时器 B 来生成 FSK 的2个频率

相关代码片段:

void set_cpu_freq () {

FRCTL0 = FRCTLPW | NWAITS_1;

CSCTL0_H = CSKEY >> 8;//解锁 CS 寄存器

CSCTL1 = DCORSEL | DCOFSEL_4;//将 DCO 设置为8MHz

CSCTL2 = SELM__VLOCLK | SELS__DCOCLK | SELM__DCOCLK;

CSCTL3 = DIVA_1 | DIVS__1 | DIVM_1;//将所有分频器设置为1

}

int main (void){

WDTCTL = WDTPW | WDTHOLD;//停止看门狗计时器

P1OUT &&~BIT3;//清除 P1.0输出锁存器以实现已定义的上电状态

P1DIR |= BIT3;//将 P1.0设置为输出方向

P1DIR &=~BIT2;

PM5CTL0 &=~μ A LOCKLPM5;//禁用 GPIO 上电默认高阻抗模式

//激活先前配置的端口设置

set_cpu_freq ();

while (1){

//消息生成代码:生成包含二进制信息的数组

__enable_interrupt ();

TA0CTL = TASSEL__TACLK | MC_1 | TACLR;// SMCLK、向上计数模式、无分频器

TA0CCR0 =(16000000/10000)- 1;//根据 SMCLK 频率设置周期

TA0CCTL0 = CCIE;//启用中断

TA0CCTL1 = OUTMOD_7;

TB0CTL = TBSSEL__SMCLK | TBCLR | MC_1;// SMCLK、向上计数模式、/8分频器

TB0CCTL1 = OUTMOD_7;

TB0CCTL0 = CCIE;//启用 CCR0中断

delay_ms (100);

}

}

#pragma vector=TIMER0_B0_vector

__interrupt void Timer0_B0 (void)

{

P1OUT ^= BIT3;//生成 FSK 频率

}

__attribute__((interrupt (TIMER0_A0_vector))//控制 FSK 信号的波特率

void timer_a0_isr (void){

if (TX_COUNTER < TXLEN){

如果(arr[TX_COUNTER]=0){

TB0CCR0 =(CPU_FREQ/(2*300000))-1;

}

否则为(arr[tx_counter]== 1){

TB0CCR0 =(CPU_FREQ/(2*400000))-1;

}

TX_COUNTER++;

}

否则{

TX_COUNTER = 0;

disable_signal ();

msp430_timer_stop ();

}

}

问题:

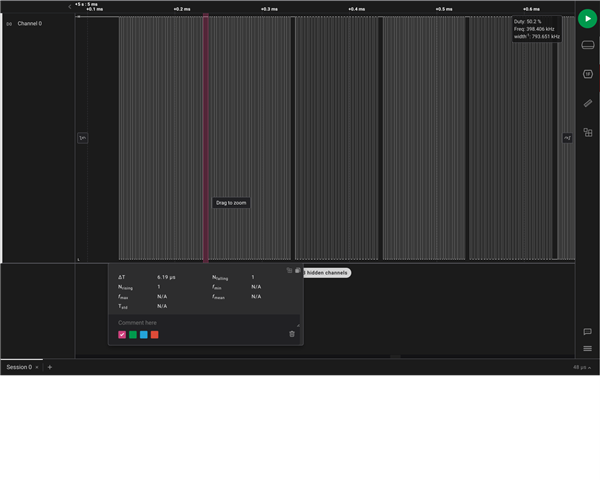

如下图所示、我观察到频率开关之间的延迟约为6-7微秒、最初我同时对计时器 A 和 B 使用 SMCLK、观察到同一个问题。 我假设这肯定是一个问题、原因是两个计时器都使用相同的源、即 SMCLK、我切换到了当前的设置、即为计时器 A 使用 TACLK、为计时器 B 使用 SMCLK、但同样的问题仍然存在、 导致波特率限制、因为6-7微秒间隙随着我增加波特率例如30kbps 变得更加显著。 我的目标是至少具有100Kbps 的波特率。

期待社区提出一些建议,以缓解这一问题。

此致!