主题中讨论的其他器件:MSP-GANG、

MSP-GANG 无法使用 BSL 对 MSP430F21x1芯片进行编程。 在加载 FBSL 或快速 BSL 后、PC 和 MSP-GANG 之间的通信会很快失败。 我在10年前的一篇文章中非常详细地描述了这个错误! 仍然没有采取任何措施来修复它。 我最近再次被这个 bug 咬了,并认为我会重新发布。

这不是临界情况、TI 的官方程序员无法使用 BSL 对离开工厂的单个 F21x1芯片进行编程。

我以前的观察仍然存在,没有任何变化,所以我不会重申所有这些,只是让读者参考我的上一篇文章。

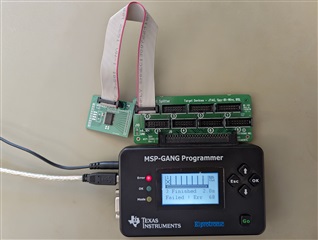

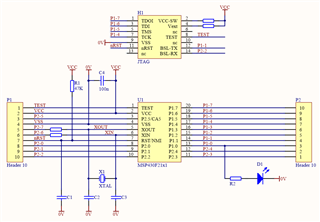

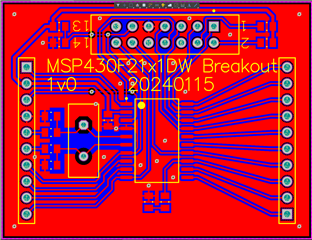

为了说明这个问题、并预先采取通常的"你做错了"响应、我已经准备了一个仅包含基本组件的板。 请参见随附的照片。

板上是 MSP430、这是一个100nF Vcc 旁路电容器。 如 slau278ah 中所指定的、一个47k 上拉电阻器和一个2.2nF 电容器在/RST 引脚上接地。

我已经组装了三块这样的板、并通过不同的方式

MSP430F2121T 修订版 E

MSP430F2131T 修订版 I

MSP430F2131修订版 K

三个电路板都存在相同的问题。 这些都是我手头的芯片版本。 我没有理由怀疑所有早期和后续的器件修订版本的行为是否相同。

JTAG 工作正常、可以读取(空白)芯片的存储器。

在加载 FBSL 后、BSL 失败并显示错误68。

我不知道我还能做些什么来说服 TI /埃尔普罗 IC 这是个真正的问题、而不仅仅是用户错误。

请修复这个错误!!!!

请修复这个错误!!!!

请修复这个错误!!!!

此致、

Sean Gallagher.

日志...

正在打开目标..DONE

………