主题中讨论的其他器件: TI-CGT

根据 MSP430优化 C/C++编译器 v21.6.0.LTS (slau132y)章节"5.7.4 volatile 关键字":"编译器不会优化对声明为 volatile 的变量的任何访问"。

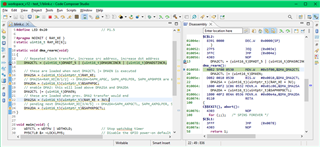

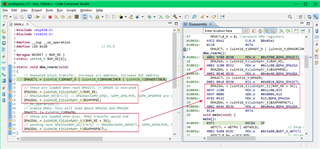

但是、当优化级别为1或更多时、以下代码会受到影响:

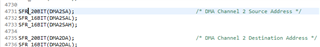

// Repeated block transfer, increase src address, increase dst address

DMA2CTL = (uint16_t)DMADT_5 | (uint16_t)DMASRCINCR | (uint16_t)DMADSTINCR;

// these are loaded when next DMA2CTL |= DMAEN is executed

DMA2SA = (uint16_t)(uintptr_t)RAM_XE; // <- THIS !!!!

// DMA2SA=RAM_XE[0/1/2] -> DMA2DA=SAPH_APGC, SAPH_APGLPER, SAPH_APGHPER are setup for consumption here (3 words per block)

DMA2DA = (uint16_t)(uintptr_t)&SAPHPGC; // <- AND THIS !!!!

// enable DMA2: this will load above DMA2SA and DMA2DA

DMA2CTL |= (uint16_t)DMAEN;

// these are loaded when prev. DMA2 transfer would end

DMA2SA = (uint16_t)(uintptr_t)(RAM_XE + 3U);

// pending next DMA2SA=RAM_XE[3/4/5] -> DMA2DA=SAPH_AXPGCTL, SAPH_AXPGLPER, SAPH_AXPGHPER are setup for consumption here (3 words per block)

DMA2DA = (uint16_t)(uintptr_t)&SAPHXPGCTL;

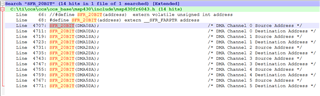

我没有找到 SFR_8BIT / SFR_16BIT / SFR_20BIT 定义、但是我认为它们应该被视为 volatile。

是否有办法让 TI 编译器不优化 DMA 寄存器访问?

谢谢!

丹尼尔

随附测试项目:

e2e.ti.com/.../test_5F00_1.zip

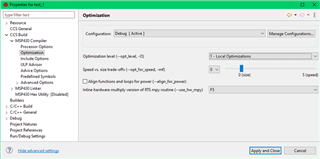

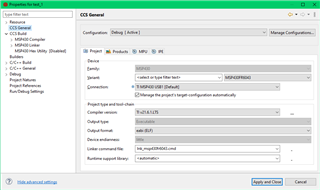

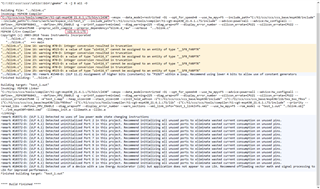

屏幕截图: