请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:MSP430FR59471 工具与软件:

您好!

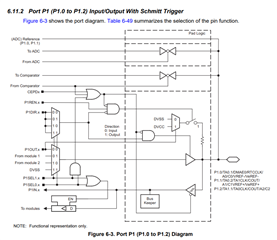

我们使用的是 TI 器件 MSP430FR59471IRHAT、并且遇到了引脚3 (P1.2/TA1.1/TAOCLK/COUT/A2/C2)问题。

我们怀疑此引脚被视为 ADC 输入、当电压超过 Vref 内部(2.5V)时、会导致测得的模拟输入(A0、A14和 A30)出现噪声和不稳定。

您能帮助我们了解如何绕过2.5V (Vref)限制、将此引脚配置为代码中的输入 GPIO 吗?

以下是我们用于引脚1.2的代码:

P1DIR &=~BIT2;

P1REN |=位2;

P1OUT &=~BIT2;

P1IES &=~BIT2;

P1IE |=位2;

感谢您的帮助!