请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:MSP430I2041 工具与软件:

大家好!

我想 ΣΔ/确认 Δ V ADC 输入电压的限制是多少。

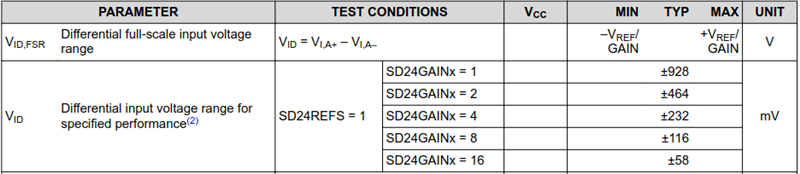

根据数据表、我看到当使用内部 VREF 时(SD24REFS = 1)、差分输入范围为(根据8.7.7.4 SD24输入范围):

当增益为1倍且内部 VREF 为1.158V (典型值)时、+/-928mV 和+/-VREF 之间存在差异。

正如第一列所示、这只是对性能要求的结果

只要输入电压保持在+/-928mV 范围内、ADC 的性能是否会如数据表中所述?

我的理解是、使用内部 VREF 时、FSR 是+/-VREF、使用外部 VREF 时为0.8*(+/-VREF)。

ΣΔ 内部 VREF、基于+/-928mV 规格、Δ Σ ADC 的最大/最小代码分别为((2^24)/2)+/-((0.928/VREF)*(2^23))。

您可以确认吗?

此致

Manos Tsachalidis