主题中讨论的其他器件:MSP432E401Y

工具与软件:

尊敬的团队:

我使用 TM4C1290和 MSP430芯片进行 SPI 通信。 TM4C 是主机、MSP430是从器件。 原始配置为模式0、时钟极性为0、相位为0。 现在两个芯片的通信模式改变为时钟极性为0、相位为1、但两个芯片无法正常通信。

MSP430相关定义:

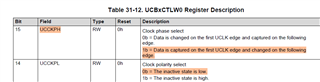

#define UCCKPH (0x8000)/*时钟相位选择*/

#define UCCKPH_H (0x0080)

#define UCCKPH_0 (0x0000)/*数据在第一个 UCLK 边沿上改变、并在上捕捉

沿。 */

#define UCCKPH_1 (0x8000)/*在第一个 UCLK 边沿捕获数据、并在上更改数据

沿。 */

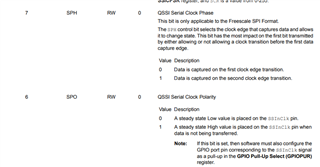

TM4C 相关定义:

#define SSI_FRF_MOTO_MODE_0 0x00000000 //模式 FMT、极性0、相位0

#define SSI_FRF_MOTO_MODE_1 0x00000002 //模式 FMT、极性0、相位1

#define SSI_FRF_MOTO_MODE_2 0x00000001 //模式 FMT、极性1、相位0

#define SSI_FRF_MOTO_MODE_3 0x00000003 //模式 FMT、极性1、相位1

//Before:

//Master:

SysCtlPeripheralEnable(SYSCTL_PERIPH_SSI1);

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOE);

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOB);

GPIOPinConfigure(GPIO_PB5_SSI1CLK);

GPIOPinConfigure(GPIO_PB4_SSI1FSS);

GPIOPinConfigure(GPIO_PE4_SSI1XDAT0);

GPIOPinConfigure(GPIO_PE5_SSI1XDAT1);

GPIOPinTypeSSI(GPIO_PORTE_BASE, GPIO_PIN_4 | GPIO_PIN_5 );

GPIOPinTypeSSI(GPIO_PORTB_BASE, GPIO_PIN_4 | GPIO_PIN_5 );

SSIConfigSetExpClk(SSI1_BASE, g_ui32SysClock, SSI_FRF_MOTO_MODE_0,

SSI_MODE_MASTER, 1000000, 8);

SSIEnable(SSI1_BASE);

//Slave:

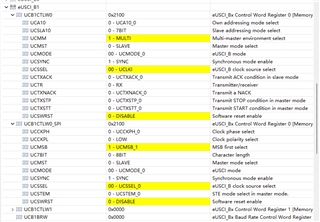

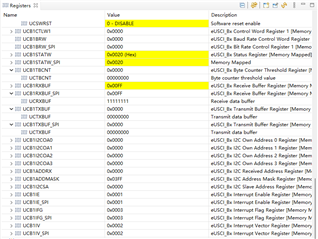

UCB1CTLW0 = UCSWRST; // **Put state machine in reset**

UCB1CTLW0 |= UCCKPH | UCCKPL_0 | UCMSB | UCSYNC| UCMST_0;

UCB1CTLW0 &= ~UCSWRST;

UCB1IFG &= ~(UCTXIFG | UCRXIFG);

UCB1IE |= UCRXIE;

//Now:

//Master:

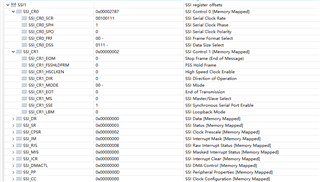

SysCtlPeripheralEnable(SYSCTL_PERIPH_SSI1);

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOE);

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOB);

GPIOPinConfigure(GPIO_PB5_SSI1CLK);

GPIOPinConfigure(GPIO_PB4_SSI1FSS);

GPIOPinConfigure(GPIO_PE4_SSI1XDAT0);

GPIOPinConfigure(GPIO_PE5_SSI1XDAT1);

GPIOPinTypeSSI(GPIO_PORTE_BASE, GPIO_PIN_4 | GPIO_PIN_5 );

GPIOPinTypeSSI(GPIO_PORTB_BASE, GPIO_PIN_4 | GPIO_PIN_5 );

SSIConfigSetExpClk(SSI1_BASE,g_ui32SysClock,SSI_FRF_MOTO_MODE_1,SSI_MODE_MASTER, 1000000, 8);

SSIEnable(SSI1_BASE);

//Slave:

UCB1CTLW0 = UCSWRST; // **Put state machine in reset**

UCB1CTLW0 |= UCCKPH_0 | UCCKPL_0 | UCMSB | UCSYNC| UCMST_0;

UCB1CTLW0 &= ~UCSWRST;

UCB1IFG &= ~(UCTXIFG | UCRXIFG);

UCB1IE |= UCRXIE;