工具与软件:

我将尝试整理 DCO-FLL 配置/校准。 我通读 UG、数据表和 MSP430FR2xx/FR4xx DCO+FLL 应用指南。

我仍然没有完全清楚。 请在下方指出我的错地方。 这将帮助我完成它!

在用户指南中:

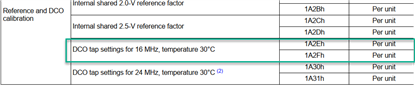

我假设下面的值(来自数据表)映射到 CSCTL0寄存器中。 16位表示16位、很适合。 对吧?

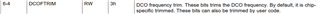

然而、根据 DCOFTRIM 位描述、它们也在总体 DCO 校准中发挥着作用。 对吧?

"特定于芯片的修整"、这是否意味着"每个独立芯片"? 如果是、我希望将这些位记录在器件描述符中。 它们是0x1A2E-0x1A30的一部分还是其他地方或不可访问并在 DCOFTRIMEN=0时自动应用?

无论哪种方式、我都假设 Dev Desc 中的 TAP 设置仅在默认 DCOFTRIM 值或 DCOFTRIMEN=0时有效。

此致