主题中讨论的其他器件:TPS40170、 LM5145

工具与软件:

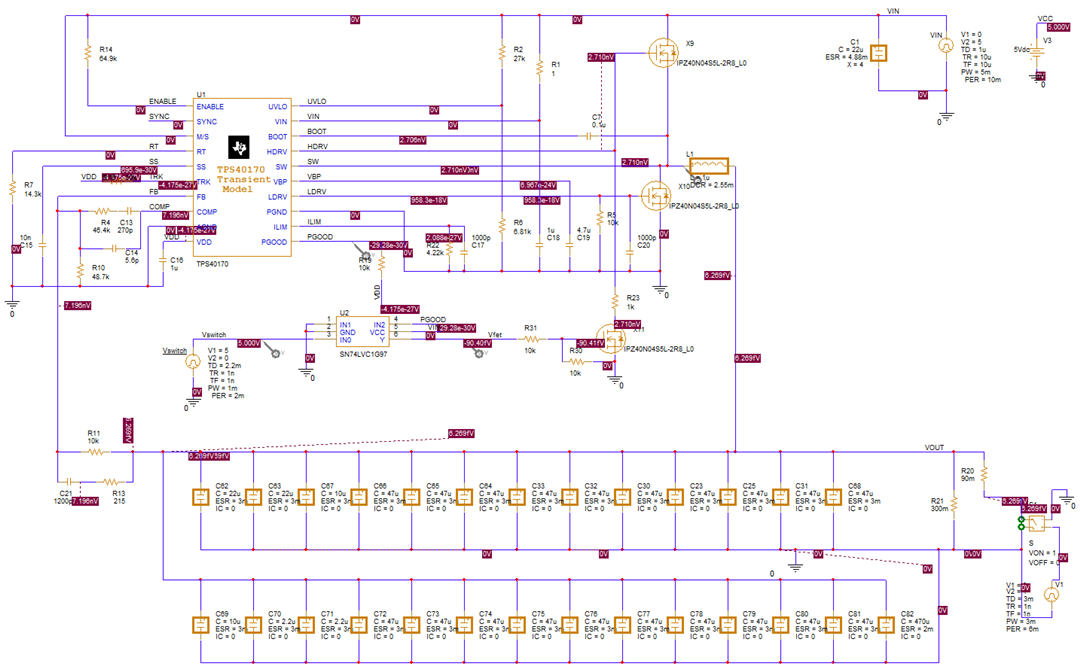

我们将在该器件的输出端实现 OVP/UVP 电路、并在故障情况下将 Hside FET 栅极拉至低电平。 使用弱下拉加载 HDRV (引脚17)是否会造成任何损害?

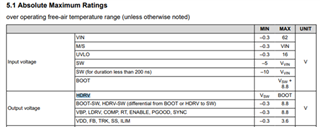

数据表显示 HDRV 的最小电压是 VSW、即-5V、所以我认为这方面比较好。 该连接是否存在任何其他问题(电流输出、SW 引脚、故障)? 仿真似乎没有暗示任何问题。

此外、我没有看到启用/禁用(引脚1)到标称 Hside / Lside FET 操作的数据表时间值、 这上面是否有任何数字? 如果禁用 Hside FET 选项无法实现、我们会考虑将其用作备份。