请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TPS3808 工具与软件:

我们将 TPS3808G01用于新项目设计。

我们的架构为:

- 我们感应到的信号、我们将其保留在安全区、您可以。 (首次上电、且> 0.405V)

我们有一些问题:

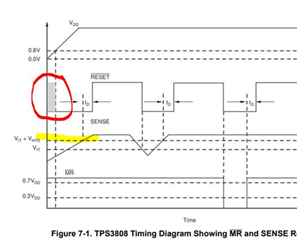

- VDD < 0.8V、是否未定义状态、对吧?

- 当 VDD 从0.8V 斜升至3.3V 时、复位引脚是否会驱动低电平?

- VDD < 1.65V、然后是复位引脚、以确保处于低电平状态、是吗?

谢谢、我们需要澄清这些要点。