工具/软件:

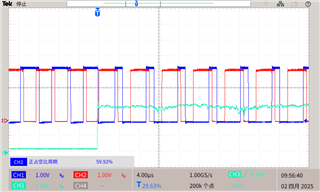

CH1:DPWM0A CH2:DPWM0B ch3:AD03

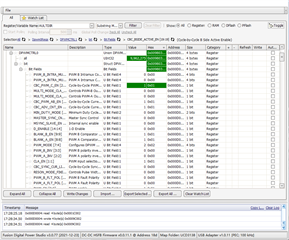

拓扑是降压。 因此、dutu 可能高于50%。DPWM 模式为 多模式。 要求 仅对 DPWM0A 使用 CBC、而 DPW0B 占空比与 DPWM0A 匹配。 DPWM 设置如下所示:

在数据表(页49表2-5)中、已设置上述寄存器。 但在测试波形中、DPW0B 与 DPWM0A 不匹配。

FaultMuxRegs.ACOMPCTRL0.bit.ACOMP_B_THRESH = 100;

FaultMuxRegs.ACOMPCTRL0.bit.ACOMP_B_SEL = 0;/*为跳闸使用阈值寄存器*/

FaultMuxRegs.ACOMPCTRL0.bit.ACOMP_B_POL = 1;/*高于 THRESH 跳变*/

FaultMuxRegs.DPWM0CLIM.bit.ACOMP_B_EN = 1;

FaultMuxRegs.DPWM1CLIM.bit.ACOMP_B_EN = 1;

您能帮助我看看哪个寄存器没有设置吗? 非常感谢!