工具/软件:

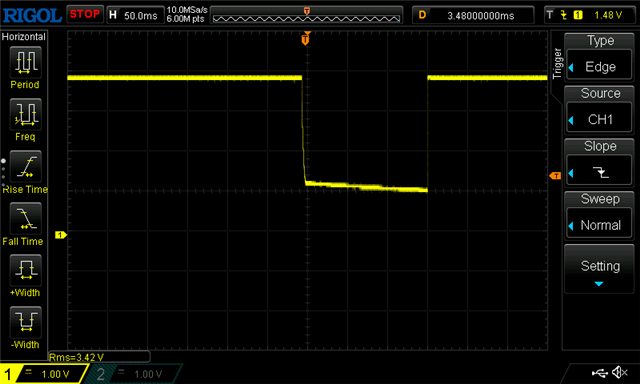

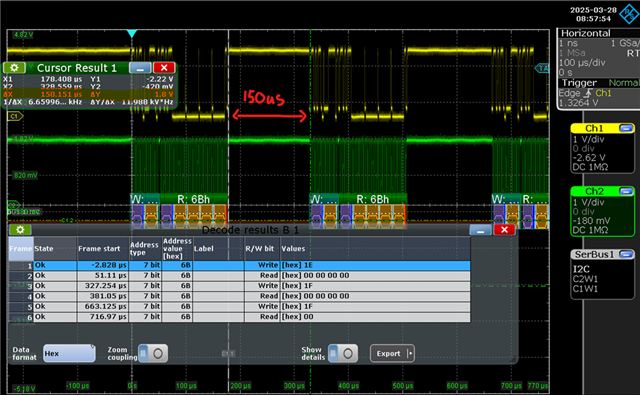

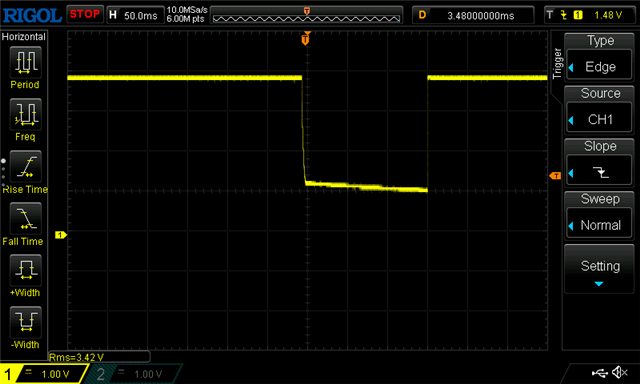

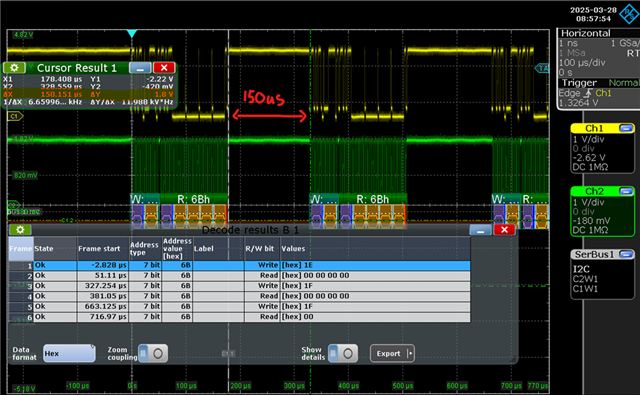

客户使用 BQ25622E 设计了电池充电器电路、 当 I2C 在标准模式(100kHz)下运行时、似乎没有问题、但当 I2C 在快速模式(400kHz)下运行时、器件无法正常工作、他们检查 BQ25622E 的 VSYS 输出是否降至约1V、持续约150us。 (请参阅下面的波形)。 它们将 tbuf 增加到100us 或更多、如下面的波形所示、但症状会继续发生。 您能否帮助提供可能导致此 问题的任何建议? 谢谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

客户使用 BQ25622E 设计了电池充电器电路、 当 I2C 在标准模式(100kHz)下运行时、似乎没有问题、但当 I2C 在快速模式(400kHz)下运行时、器件无法正常工作、他们检查 BQ25622E 的 VSYS 输出是否降至约1V、持续约150us。 (请参阅下面的波形)。 它们将 tbuf 增加到100us 或更多、如下面的波形所示、但症状会继续发生。 您能否帮助提供可能导致此 问题的任何建议? 谢谢!

您好、Eric、

为了防止出现所述的 VSYS 下降行为、BQ25622E 器件对 I2C 通信具有时序要求。 数据表第8.5.1节介绍了该要求。 使用标准模式(100kHz) I2C 时无需额外要求、因此客户没有发现问题。

以400kHz I2C 运行时、至少需要68us Tbuf。 虽然提供的波形确实显示两个通信数据包之间有足够的 tbuf 延迟、但我想指出的是、I2C 读取事务包括通信中的第二个启动命令。 执行读取时、I2C 读取的第1个 START 命令和第2个 START 命令之间需要有足够的延迟。 提供的波形在读取过程中似乎没有此类延迟。

如果客户认为他们正在正确实现此必要的延迟并且仍然发现问题、您可以让他们共享一个显示同一捕获中的 SCL、SDA 和 VSYS 的波形。

此致、

Garrett