工具/软件:

你好

我们在设计中包含了 TSP26633。

在电路板的初始启动期间、我们已尝试在电路板上执行过流测试、以验证 TPS26633是否关断电流到电路其余部分。

遗憾的是、当超过电流限值时、TPS26633会很快过热、并在几秒钟内捕捉到火灾。 现在在2个单独的板上看到了这种情况。

IC 烧毁时的负载电流为4.6A、即100mA 上的电流高于电流限制阈值。

测试期间使用的负载是将电子负载设置为4.5A 的情况。 使用热像仪对4.5A 进行了测试、温度未达到40°C 上的任何点。

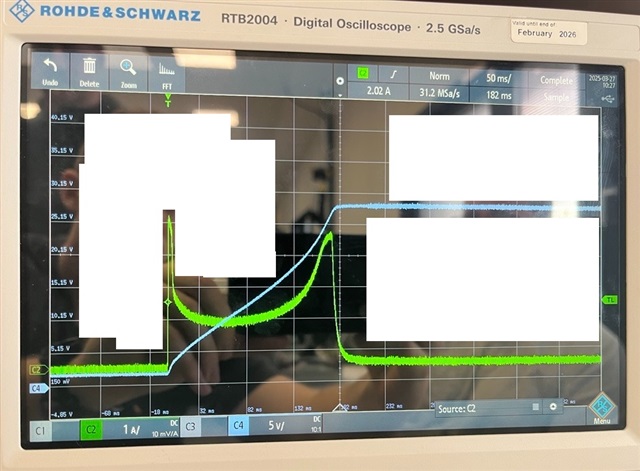

下一项测试是将负载提高到4.6A、使其完全关断。 发生了关断、但在自动重试期间、IC 开始烧录。

测试期间的负载电容为12mF。 浪涌电流也是在启动时测量的(SHDN 置为无效)、这与 TPS2663数据表中的图8-4非常匹配、初始峰值为4.5A

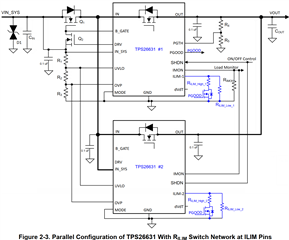

原理图如下所示:

请告知为什么会发生这种情况?