Other Parts Discussed in Thread: TPS274C65

工具/软件:

尊敬的支持团队:

我们的定制 PCB 板上有四个连接到同一 SPI 总线的 TPS274C65芯片。 两个芯片使用其内部稳压器、其中 VS 输入由+24V 供电并由电子保险丝提供保护。 另外两个芯片由外部+3V3稳压器通过其 VDD 引脚供电。 其 VS 输入也由+24V 供电并由电子保险丝提供保护。

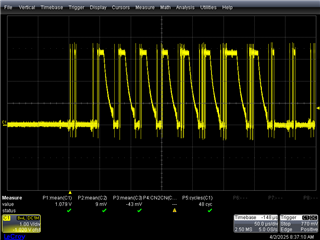

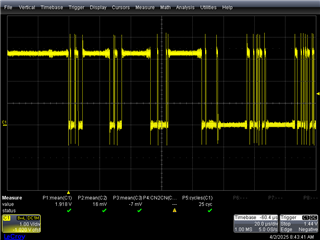

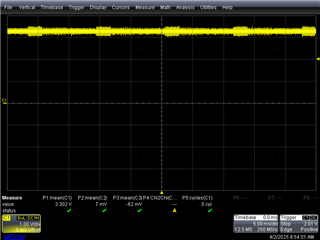

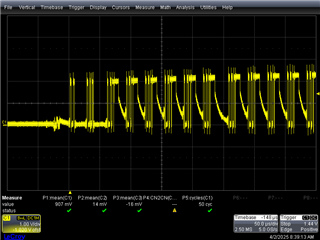

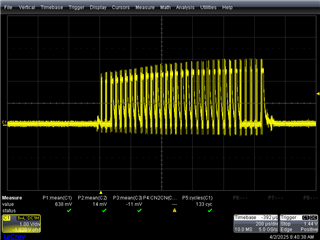

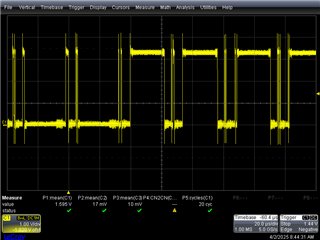

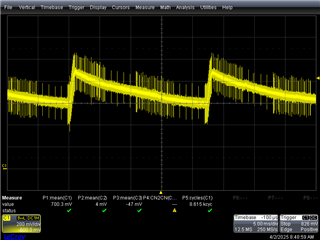

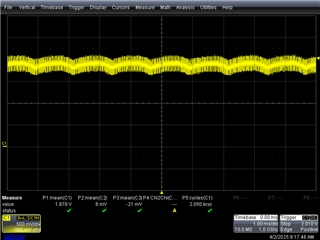

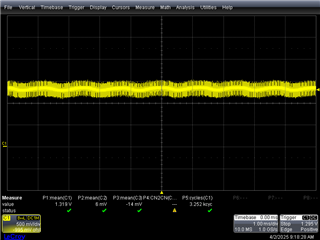

当所有四个芯片均通电时、微控制器和 TPS274C65芯片之间的 SPI 通信工作正常。 如果具有内部稳压器的 TPS274C65芯片没有 VS 电源、则会影响同一 SPI 线上的所有其他有源 TPS274C65芯片、使其无法正常工作。 这个未提供的芯片可能会拉低 MISO 线路的数据信号。 在这种情况下、有源 TPS274C65芯片发送的高电平信号不会超过微控制器的高电平电压阈值、因此无法正确验证。

如果两个 TPS274C65芯片未通电、则与所有四个芯片均通电的信号相比、MISO 线路上的压降至少为300mV。

该电压下降影响 MOSI 线路上的数据流量。 使用小电流值时、高电平 约为+2V、而大电流值约为+3V。

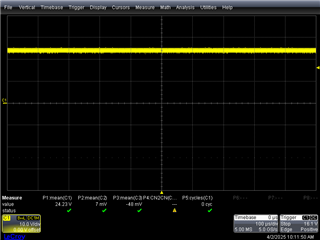

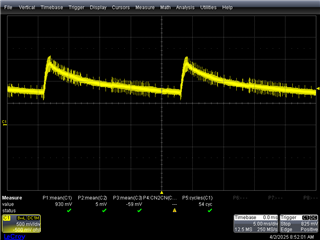

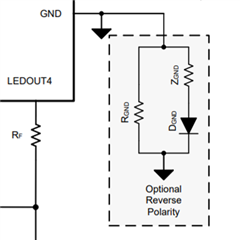

未上电的 TPS274C65芯片 VDD 引脚上电压信号的测量结果显示、电容充电和放电信号高达+2V 、频率周期 对应于 SPI 通信轮询时间。

这是 TPS274C65芯片所需的/已知行为吗?

为避免这种行为、建议采用哪种解决方案?

提前感谢。

此致、

Aron