线程中讨论的其它部件:AM6442, TPS745,

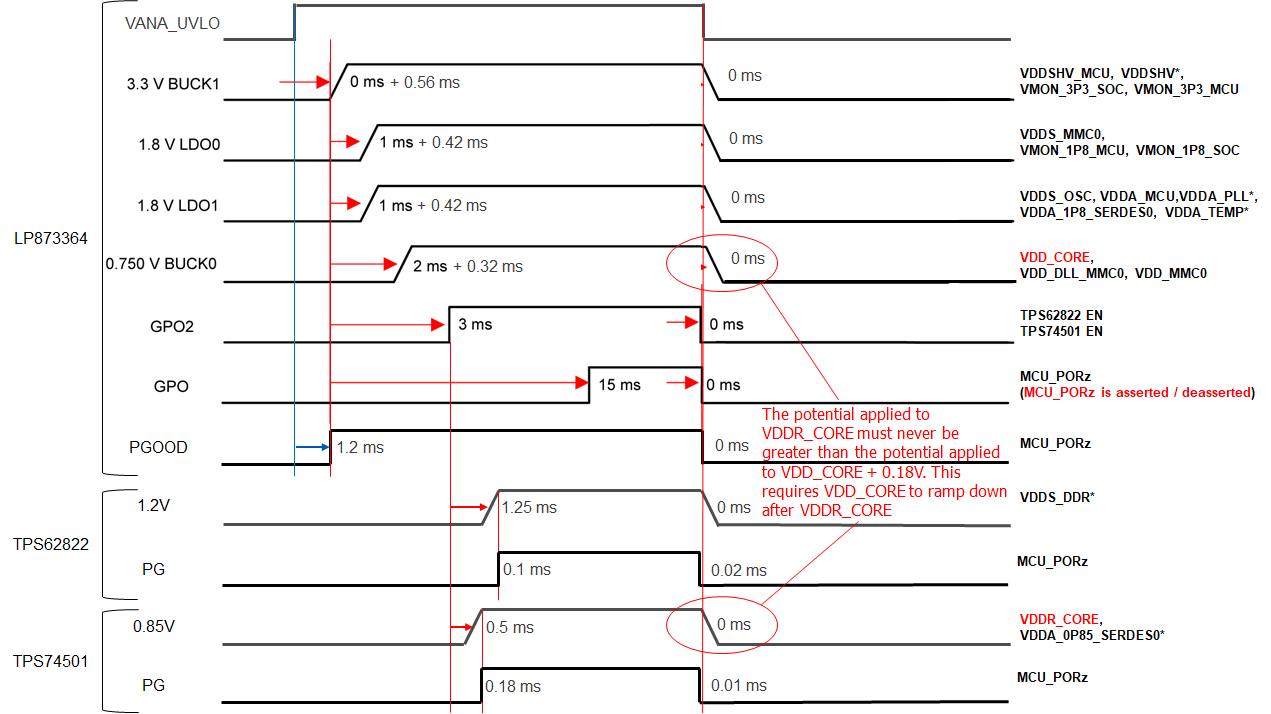

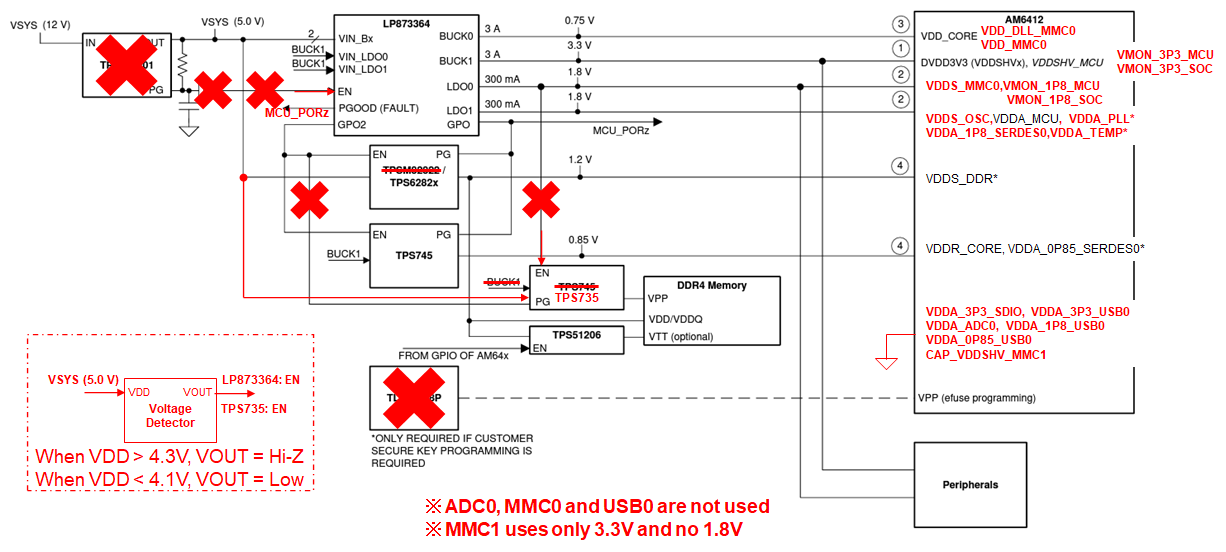

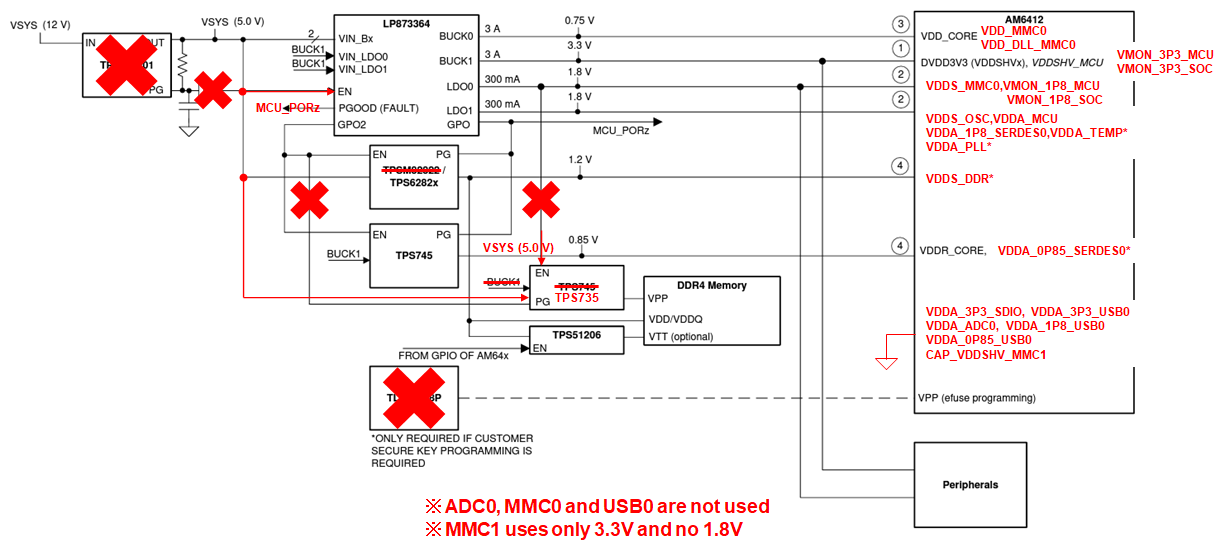

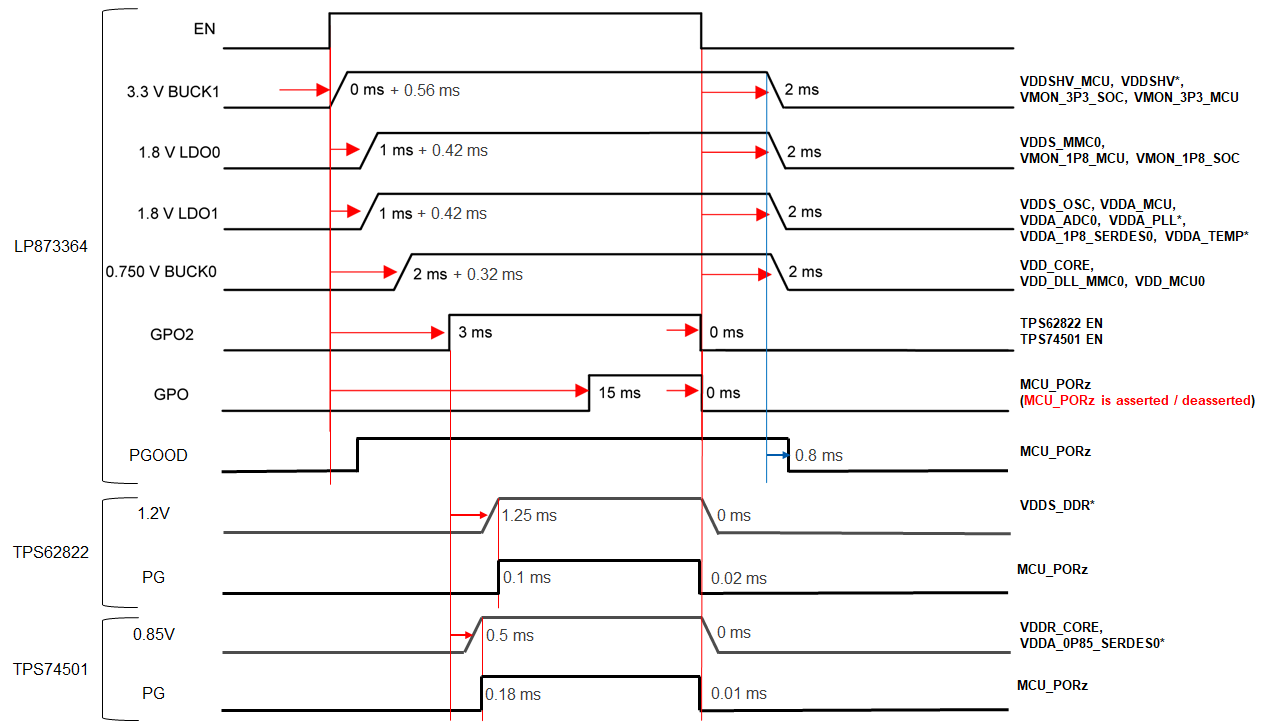

我们的客户正在设计采用 AM6442 SR1.0的原型板,并使用 LP873364为 AM6442提供动力。

EN 引脚能否与 Vana 和 VIN_Bx 电源引脚一起连接至 vsys (5V)? 如果没有,应该如何连接 EN 引脚?

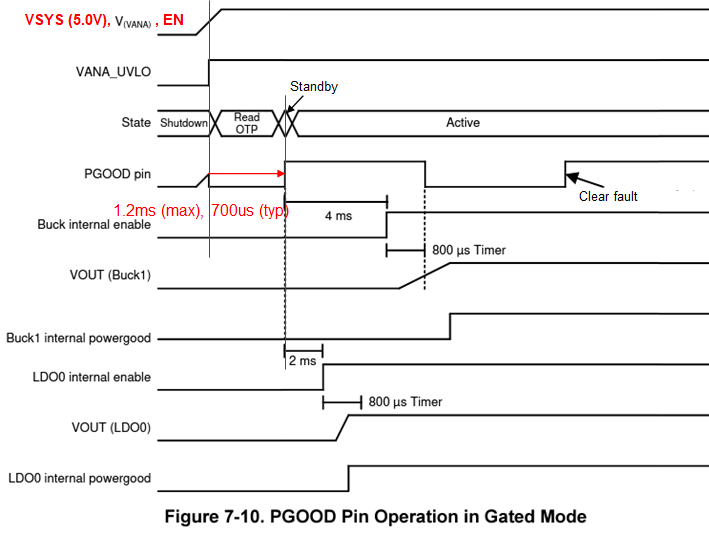

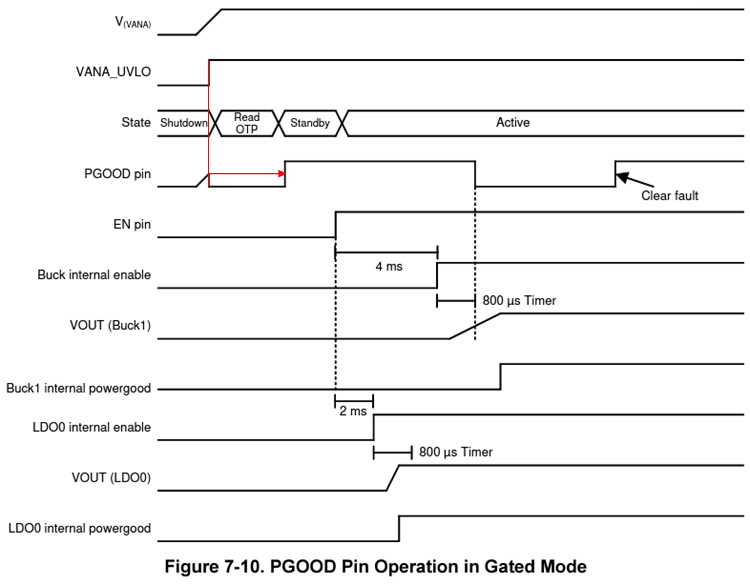

当退出 OTP 配置为初始默认状态时,PGOOD 被设置为活动或断言状态。

高于 VANAUVLO 阈值级别的 V(Vana)电压与正在断言的 PGOOD 针脚之间的延迟是多少?

我们的客户将 PGOOD 引脚连接到 AM6442的通电重置引脚(MCC_PORz)以及 GPO 引脚和其他电源 PG 引脚。

在正常和故障条件下,此连接是否能够正常工作以重新启动 AM6442? 如果没有,应如何连接 PGOOD 引脚?

此致,

黛西克