大家好,团队

请帮助回答以下问题?

描述为“使用的 VSET/模式电阻器的延迟时间各不相同,最长电阻为249 k 或更高”

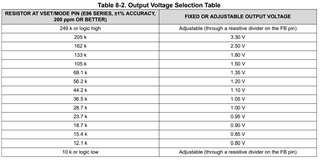

还有一个表格,如下所示:

所以我在这里有点困惑,例如,我想要一个0.90V 输出, 我应该在 Vset/模式引脚处选择一个18.7k 电阻器。

问题1. 我的 tdelay 是否会是一个匹配的延迟时间,对吗?

问题2.如果问题1答案为“是”,那么在一个输出电压条件下,只有一个延迟时间,这一延迟实际上不可调整?

问题3. 如果 Vset 引脚为0.90V,那么 Vset/模式逻辑值过低,因此该部件必须在 PSM 下工作?

谢谢

此致

美麻