您好,TI团队:

我有一个与TPS546A24A的EN引脚相关的查询。 I Wan,通过使用值(R1233-10K和R1022- 6.04K)通过硬件(EN引脚)启用带分压器的电脑控制器。 Voltage_en= 1.88V

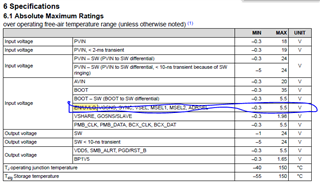

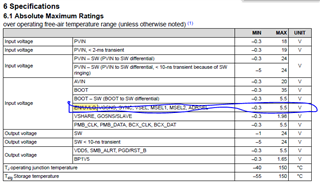

EN的绝对最大额定值为- 0.3 至5.5V,电气特性为1.05 至1.1V。

那么,有人能建议我们可以为EN引脚保留什么电压来打开调节器吗?

此致

Kapil

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,TI团队:

我有一个与TPS546A24A的EN引脚相关的查询。 I Wan,通过使用值(R1233-10K和R1022- 6.04K)通过硬件(EN引脚)启用带分压器的电脑控制器。 Voltage_en= 1.88V

EN的绝对最大额定值为- 0.3 至5.5V,电气特性为1.05 至1.1V。

那么,有人能建议我们可以为EN引脚保留什么电压来打开调节器吗?

此致

Kapil

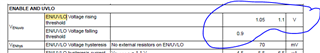

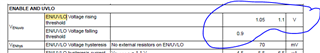

电气规格表提供EN/UVLO引脚从禁用转换为启用的电压。 在上升转换时,这介于1.0V和1.1V之间,典型值为1.05V。

EN/UVLO引脚上允许的最大电压为5.5V。

通过EN/UVLO引脚上的10k / 6.04k分压器,TPS546A24A将尝试在2.65V和2.92V之间打开,内部5μA Ω 电流在EN/UVLO引脚的70mV内部电压滞后的185mV之上提供额外的50mV滞后。

但是,如果Avin由PVIN输入供电,而VDD5不由单独的电源外部供电,则在Avin和VDD5上升至4.0V以上之前,转换将不会启用,因此EN/UVLO引脚将不会提供UVLO功能。

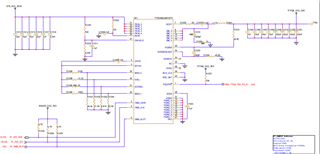

我还注意到,您的示意图显示了从PVIN到Avin的10Ω Ω 电阻器。 对于5V输入,我建议使用更小的电阻器和更大的电容器,以获得推荐的10μs μ s时间常数,从而减少电阻器的压降。 我看不到您的切换频率,但在操作过程中,Avin电流大约为10mA + 5mA (每100kHz切换频率)。 (500kHz时为35mA),可导致PVIN至Avin电阻器的显著电压降。

此外,对于不超过5.5V的5V输入,也可以向VDD5提供5V输入,从而消除了从Avin到VDD5的LDO输出,并提高了栅极驱动电流和效率。

您好Peter,

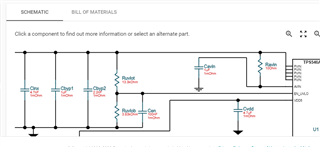

感谢您的澄清。 那么您对EN引脚分压器有何建议? 我在 WEBENCH 电源设计器中看到 的值是13.3K和3.83K。 我是否应该使用此值?

对于10E电阻器,它在 工作台中显示相同的时间值。 那么,应该遵循Web工作台设计吗?

对于切换频率,我们将采用450KHz。

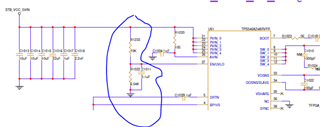

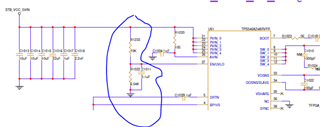

分享设计供您参考(输入5V和输出为 3.3V@1.5A)。

此致

Kapil

电阻器的尺寸应基于所需的滞后水平和保证开启的最小PVIN电压。

要设置保证打开的PVIN电压,请调整电阻分压器的尺寸,以便在最低的VIN处提供1.05V电压,从而保证打开。 对于3.83kΩ Ω 和13.3kΩ Ω,在VIN达到4.7V之前TPS546A24A可能不会打开 。如果可以接受,则这些电阻值正常。

要选择绝对电阻,请考虑关闭。 TPS546A24A将提供5μA μ A的电流并降低阈值电压70mV。 70mV针脚阈值变化将提供328mV的滞后,而5μA Ω 电流源将提供66mV的滞后,总共为394mV。 如果您需要更多滞后,请按比例增加两个电阻器的值以增加滞后。

对于PVIN至Avin电阻器,在450kHz切换频率下具有5V输入,电阻器之间可能会出现250-300mV的压降,这将限制栅极驱动电压。 它将起作用,由于这是一个低于10A的应用,因此下部栅极驱动电压的效率影响可能不是关键。 但是,我通常会推荐使用2.2Ω Ω 电阻器和4.7μF Ω 电容器作为5V输入建议。

您好Peter,

感谢您的澄清。

对于1.05 ,我们讨论的是典型值,现在它也取决于电阻器容差。 所以我想我应该把电压分配器设为1.1V。 您对此有何建议?

这意味 着对于3.83kΩ Ω 和13.3kΩ Ω,TPS546A24A可能在VIN达到4.7V之前不会打开(它在通过4.7V直流之前受到电压保护?)。

来自MPU/FPGA的12V输入和稳压器EN控制如何?

我是否也为这种情况调谐10欧姆电阻? Vdd5引脚也会发生什么情况?

此致

Kapil

我在计算中使用了1.1V,这也是为什么我也得出了4.7V。

在EN/UVLO高于其阈值电压之前,TPS546A24A的输出将保持关闭,转换器处于“欠电压锁定”状态

要添加EN/UVLO的MPU/FPGA控制,您可以在EN/UVLO级别添加漏极开路下拉列表,以强制EN//UVLO引脚低于其阈值,然后释放它以跟随电阻器分配器,从而在同一引脚上提供Enable和UVLO功能的组合。

除非外部供电,否则VDD5将跟踪低于Avin或4.7V的50-100mV的较低值。