主题中讨论的其他部件: TINA-TI

您好,先生,

我向您学习,

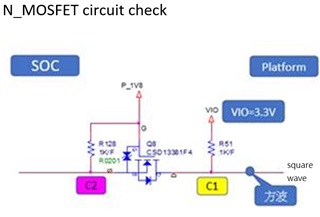

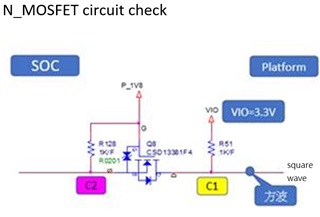

请参阅以下NMOS电路图,向漏极(点C1)输入方波,并从3.3V=>0.1V,3.3V=>0.2V,3.3V=>0.3V直至3.3V=>1V输出低电压

同时,观察源端子(点C2)的变化,从图中可以看出,当点C1为3.3V=>0.7V时,点C2处的偏移电压差相对明显(与点C1处的电压相比)

这是什么现象? 如何解释存在偏移电压差异,感谢您的帮助。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,先生,

我向您学习,

请参阅以下NMOS电路图,向漏极(点C1)输入方波,并从3.3V=>0.1V,3.3V=>0.2V,3.3V=>0.3V直至3.3V=>1V输出低电压

同时,观察源端子(点C2)的变化,从图中可以看出,当点C1为3.3V=>0.7V时,点C2处的偏移电压差相对明显(与点C1处的电压相比)

这是什么现象? 如何解释存在偏移电压差异,感谢您的帮助。

您好Tommy,

感谢您的咨询。 我运行了TINA-TI模拟(随附)。 通常,当放电电压变为0V时,VGS = 1.8V,FET打开,VDS ~ 0V。 随着低电平的增加,此电压将从VGS中减去。 在0.1V时,VGS = 1.8V - 0.1V = 1.7V。 您可以看到每个步骤的偏移量都在增加。 最终,当低电平约为0.7V且VGS应为1.1V时,由于FET未完全打开且通道不再支持漏电流,VDS中的压降随着接近阈值电压而开始增加。 如果有任何负载电流通过FET,则偏移将更大。 我不确定此测试的目的是什么。 但是,如果如原理图所示将CSD1.3381万F4用作高压侧负载开关,则必须将栅极拉至高于排放阀至少1.8V的位置,以保证FET的电阻。 如果您有任何疑问,请告诉我。

此致,

约翰·华莱士

TI FET应用