我正在开发一种应用,它使用LM3409驱动8个LED条带,组合压降为25V,28V电源的电流消耗为360mA (+- 25 %)。 我的目标频率是462khz,~120ns。 我已从数据表数学计算中为我的无能元件得出以下值:

占空比@ 95 % 效率:25 /(0.95 x 28)= 0.94

Toff:-28 (4.7e-10 + 2e-11) x Ln (1 -(1.24 / 25))= 1.3E-7

FSW:(1 - 0.94)/ 1.3E-7 =~46.2万

Roff:5.2kΩ

IMAX = 0.36 +(0.36 * 0.25)= 0.45

Rsense:1.24 /(5 x 0.45)~0.55Ω

我还使用了47µH Ω 电感器,它比所需的大,但由于与装配体定价方式相关的原因,我降低了成本。 为了测试我的设计,我创建了一个布局,它基本上与LM3409评估板重复,但使用我自己的无源器值。 我遇到的问题是主板为LED供电的电流比Rsense应该产生的电流低得多。 Ω 进行健全性检查,我将Rsense换成了评估设计中使用的0.2 电阻器,尽管 VIADJ控件非常非线性,但该板发出了正确的电流。

使用0.55Ω 的检测时,我看到的值为~10mA,大大低于我应该看到的360mA。

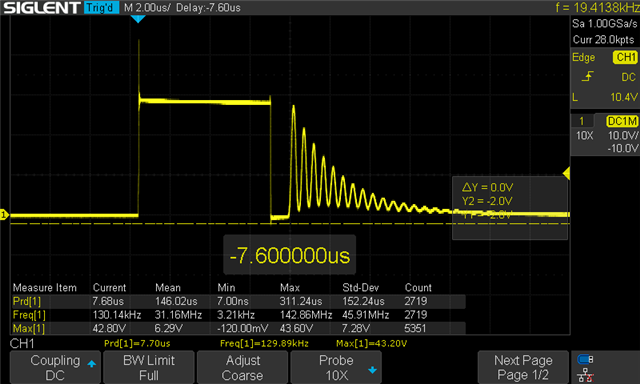

我用示波器进行了一些测量,这就是我所看到的:

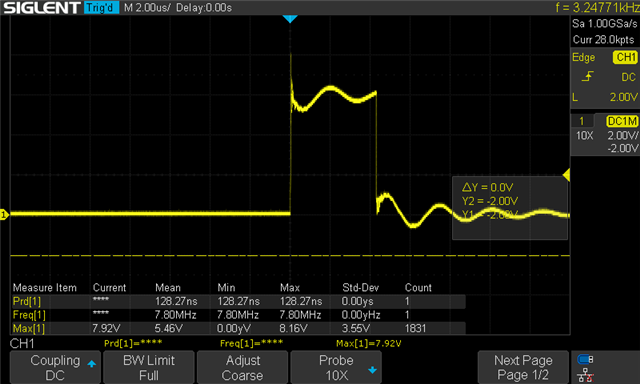

当示波器探针接地在PFET的门上,探针在源上时,我看到大约130ns的脉冲, 这让我认为正时设置正确。

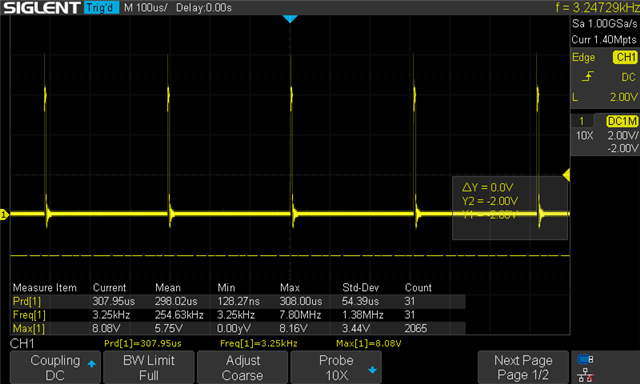

但~似乎是在300µs º 水平上,将总频率设置为 º 3.25khz。 根据数据表中的数据,Toff由测量Rsense上的压降来确定。

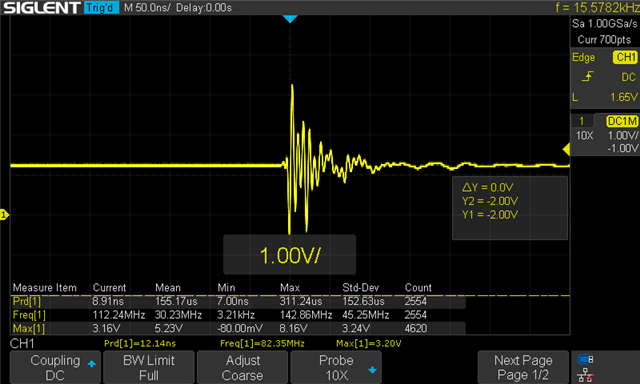

当探针接地位于电路接地,探针位于SW节点上时,我会看到一些振铃,但我不确定这会导致我所看到的问题。

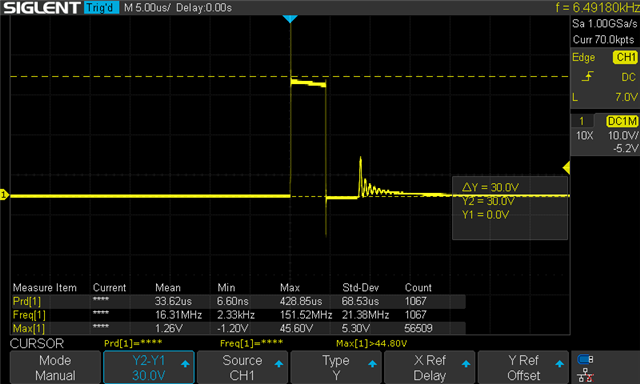

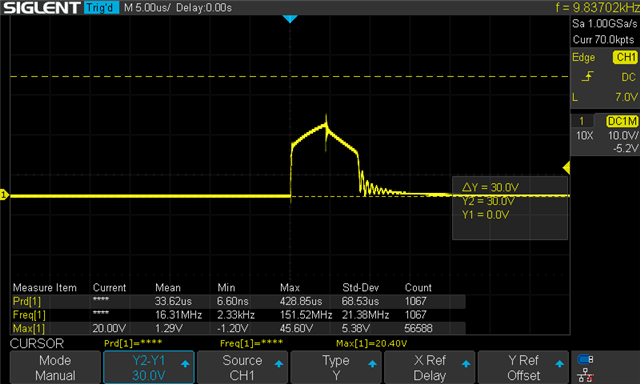

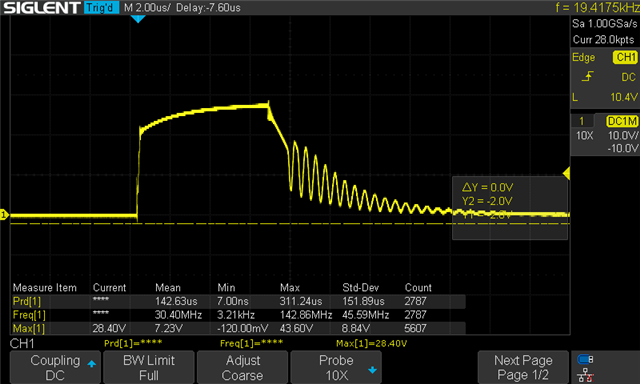

在Vout上使用探针时,峰值电压看起来是正确的,但脉冲又太短,无法产生所需的电流输出。

为了进行健全性检查,我检查了VIADJ,我看到了一个奇怪的脉冲,我认为是来自电路中其他地方的噪音。 但是,在我的数字万用表上,电压读数为1.23V。

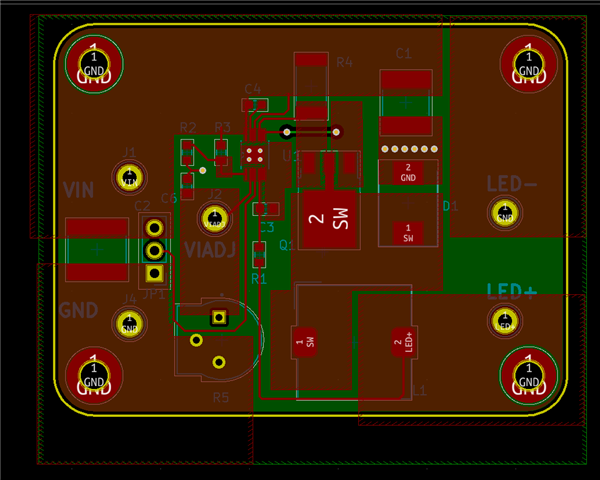

这是我的主板布局,您可以看到它是否是从评估设计中衍生出来的。