主题中讨论的其他部件: UCC2.7614万, UCC2.7322万

我需要一个闸极驱动器用于前端功率放大器开关应用- 功率MOSFET 通过 配置为高端开关的p通道MOSFET来开关PA的漏极偏差。 我曾考虑使用UCC2.7516万/7,但应用描述仅提及低侧使用。 据我所了解,这似乎不是为什么不能用于高端P通道MOSFET的原因。 实际上,Spice模拟似乎显示,当我将设备设置为反相模式时,它可以工作。

我错过了什么吗? UCC2.7516万/7的性能是否会在某种程度上不受欢迎?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

我需要一个闸极驱动器用于前端功率放大器开关应用- 功率MOSFET 通过 配置为高端开关的p通道MOSFET来开关PA的漏极偏差。 我曾考虑使用UCC2.7516万/7,但应用描述仅提及低侧使用。 据我所了解,这似乎不是为什么不能用于高端P通道MOSFET的原因。 实际上,Spice模拟似乎显示,当我将设备设置为反相模式时,它可以工作。

我错过了什么吗? UCC2.7516万/7的性能是否会在某种程度上不受欢迎?

您好,Ryan:

感谢您联系E2E!

您确实可以将低侧驱动器用作高侧开关! 有关将其用作高端交换机的常见问题解答的链接可在此处找到: https://e2e.ti.com/support/power-management-group/power-management/f/power-management-forum/108.292万/faq-ucc27624-can-i-use-a-low-side-driver-as-a-high-side-driver?tisearch=e2e-sitesearch&keymatch=driving%25252525252520a%25252525252520pmos%25252525252520with%25252525252520low%25252525252520side#</s>27624 2525252525252025252525252520252525252525202525252525252025252525252520

但是,使用PMOS交换机时需要考虑一些因素。 在UVLO事件期间,驱动器的输出保持低电平,这将使PMOS保持打开,从而导致开关烧坏。 在这种情况下,建议不要使用PMOS开关。

您能否向我提供您的设计示意图? 通过这种方式,我可以查看并为您提供一些优化高端切换的建议。

谢谢!

Kevin

您好,Kevin:

感谢您的回复。 这也是一个有用的链接。

你关于UVLO的观点是公平的,虽然我没有这么多,但我认为在这份申请中可能可以接受。 要明确一点,这不适用于调节器设计。 我们使用PMOS来快速打开和关闭前端放大器。

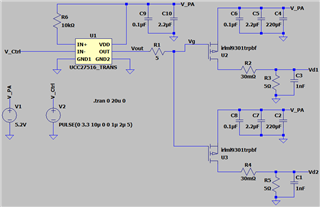

这是Spice模型的快照。 请原谅我使用LTSpice,哈哈。 没有什么可反对TINA或TI PSpice (我 也使用它们),我只是碰巧已经为这些设计设置了LTSpice。

您好,Ryan:

感谢您的耐心等待!

关于当前设计,我有一些建议。

首先,我强烈建议您不要使用PMOS FET,而是将它们切换到NMOS FET。 几乎所有现代的日间门驾驶员都有UVLO保护,这将导致上述问题,在UVLO事件期间PMOS始终处于打开状态。

切换至NMOS FET,必须将耗散 电阻器R5和R3移至开关上方。 如果您在NMOS开关下方保持较大的电阻,则可能会出现压降,从而降低栅极至源电压(Vgs)。 假设我们有一个FET,接通电压为10V。 如果您应用10V来打开FET,并且该电阻器上有5V压降,则您的Vgs将为5V,这不足以完全打开FET。

当并联两个开关时,您应该为每个FET实施一个栅极电阻器。 为每个MOSFET提供其自己的栅极电阻器,而不是为所有并联MOSEFT提供一个栅极电阻,从而最大程度地降低单个MOSFET将噪声耦合到彼此栅极的能力。

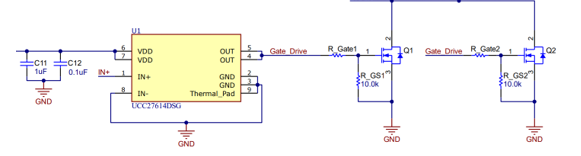

以下是使用UCC2.7614万和两个并联MOSFET的示例。

基于另一个螺纹,UCC2.7614万将是您在驱动强度方面的最佳选择,因为您将与这两个NMOS FET并联,它们将使栅极驱动负载电容翻倍。 目前,您可以将UCC2.7322万 SPICE模型用作模拟工具。 只需注意UCC2.7322万可吸入和源9A/9A,UCC2.7614万可吸入和源10A/10A。

如果您还有其他问题或希望进一步解释,请告诉我。 我很乐意帮助您进一步了解这款或任何其他TI低侧/GAN栅极驱动器!

谢谢!

Kevin