大家好、

我想尽可能降低待机电流、因此我想增大 EN 引脚上的下拉电阻值。

1) 1)您能否建议使用最大的下拉电阻(最小下拉电流)来保持 EN 引脚处于低电平?

2) 2)如果 EN 引脚开路、则 FMA 引脚的行为描述如下。

"不确定的器件操作;器件可能加电或未加电"

在我的情况下、电源由悬空 EN 供电、然后1ms 后、通过 MCU 将 EN 引脚驱动为高电平。

在这种情况下、器件将从不确定的器件操作中恢复?

或者器件是否有电势保持关闭?

此致、

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、

我想尽可能降低待机电流、因此我想增大 EN 引脚上的下拉电阻值。

1) 1)您能否建议使用最大的下拉电阻(最小下拉电流)来保持 EN 引脚处于低电平?

2) 2)如果 EN 引脚开路、则 FMA 引脚的行为描述如下。

"不确定的器件操作;器件可能加电或未加电"

在我的情况下、电源由悬空 EN 供电、然后1ms 后、通过 MCU 将 EN 引脚驱动为高电平。

在这种情况下、器件将从不确定的器件操作中恢复?

或者器件是否有电势保持关闭?

此致、

您好、Shinji、

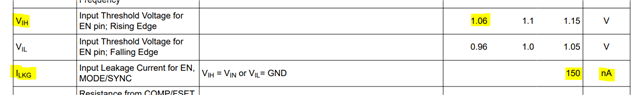

参考数据表、我相信我们可以将系统估算为 流经下拉电阻器的泄漏电流。

因此、理论上、您需要一个低于1V/150nA ~ 6.67MOhm 的电阻器。

请记住、在实际应用中、您可能在同一条布线上连接了其他元件(例如 MCU 的 GPIO)、因此您还应在漏电计算中考虑它们的影响。

最后、我会留出一些裕度来包含布局寄生、并处于安全侧。 我们仍建议在最终 PCB 上测试该值以确认这些计算。

关于您的第二个问题、虽然在理想世界(或 EVM)中它不应该成为问题、但在有噪声的系统中、外部噪声可能会多次触发 EN 引脚悬空、并且很难预测此行为对转换器的影响。

我建议不要像数据表中建议的那样使引脚悬空。

谢谢、

Stefano