请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:UCC21750QDWEVM-025 主题中讨论的其他器件:UCC21750-Q1

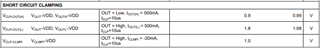

在 UCC21750-Q1的数据表中、有三个短路钳位项。 (VCLP_OUT (H)、VCLP_OUT (L)、VCLP_CLMPI)(第10页)

我想知道这些项目中测试条件的含义。

对于 VCLP_OUT (H)、我理解为当输出电平为低电平时、500mA 电流流经 OUT 引脚、10us 后、输出电压减去 VDD 等于0.9V (典型值)。

对吗? 由于我不确定短路钳位电路、因此不确定我是否理解良好。

此致、

Kim Yoonjin