Other Parts Discussed in Thread: TPS63070, TPS3702, TPS3840

主题中讨论的其他器件: TPS3702、 TPS3840

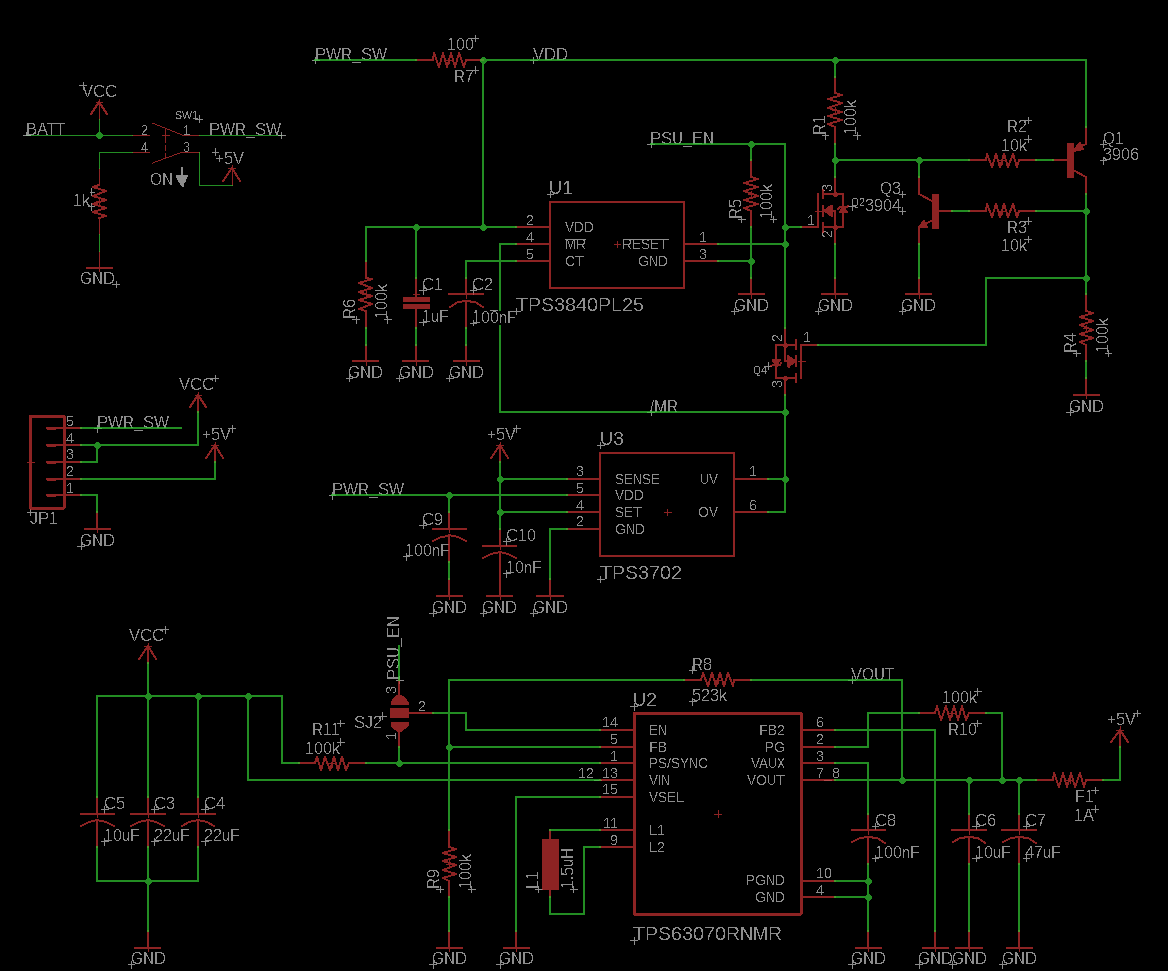

我正在尝试使用 TPS63070降压/升压转换器、使用4节 AA 电池供电的5V 电源。 为了避免启动回路、我希望在电池电压开始崩溃时关闭输出、因此我使用 TPS3840PL25将 TPS63070上的 EN 线拉低、并使用以下注 释中所述的电路将其锁存:https://www.ti.com/lit/an/snva836a/snva836a.pdf

这很好。 但是、我还想在5V 输出上添加一个监控器 IC、以保护系统下游、主要是防止出现输出过压情况。 我尝试用我的设置来实现这一目的的最佳方法、并确定添加 TPS3702来监控5V 线路、允许它在错误状态下将 TPS63070上的 EN 引脚锁存为 OFF、这是一个不错的选择。

在此原理图中、VCC 是电池直接产生的电压。 插入电池后、首先会禁用降压/升压(通常会焊接 SJ2、因此 EN 引脚连接到 PSU_EN、添加这些跳线以进行故障排除)。 一旦开关打开(SW1)、电池电压被施加到 TPS3840、 一旦达到上电阈值、/RESET 线路被拉至高电平、这将打开降压/升压。 (注意:在某些下游负载的启动序列期间添加了 R7/C1毛刺保护、以防止错误的闭锁)。

为了添加5V 窗口监控、我的想法是在5V 线路超出稳压范围时、将 TPS3840上的/MR 线路拉低、并在 TPS3702上提供 UV 和 OV 输出 (或者、当用户为反馈电阻器输入错误的值并且在组装其余组件之前忘记检查输出时)。 根据 TPS3702数据表、UV 和 OV 引脚应上拉、但/MR 引脚具有内部100k 上拉电阻、因此我将依赖它。 我相信、在5V 线路错误状态下拉低/MR 将启用锁存电路、最终关闭 TPS63070、直到电源开关循环以复位锁存器。 我最初担心这样做可能会导致 VDD 接地短路(当/RESET 为逻辑高电平时、Q4导通、OV/UV 被拉至逻辑低电平)、但我不认为这是实际情况、因为只要/RESET 处于 VDD、Q4就会关闭。 但是、当 OV 拉低且/RESET 仍处于 VDD 时、我是否需要担心暂时通过 Q4体二极管导通?

这是一个准确的评估吗? 这种策略是否有明显的缺陷?

我的另一个问题是启动时的行为。 TPS3702的启动延迟为300微秒。 我的问题是、这种延迟时间何时开始? 数据表中的图1似乎意味着它在达到 VDD (min)后? 还是与感应引脚相关? 目前、TPS3840的 CT 引脚上有一个100nF 电容器、用于在电源开关接通后延迟启用 TPS63070大约60毫秒。 因此、如果 TPS3702上的 VDD 超过 VDD (min)、欠压感测是否会自动触发?

谢谢!