尊敬的支持论坛:

在反激式 SMPS 中使用 UC2844获取干净的栅极信号时遇到问题。

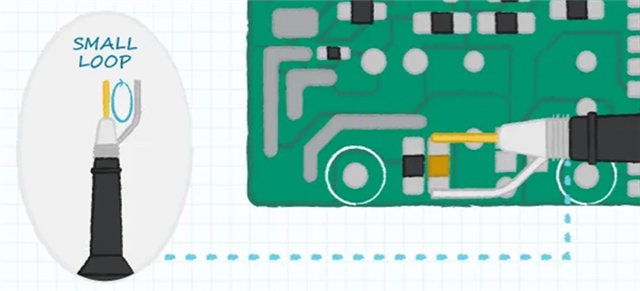

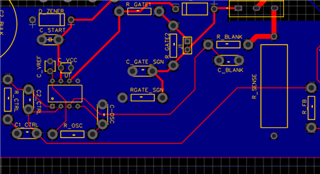

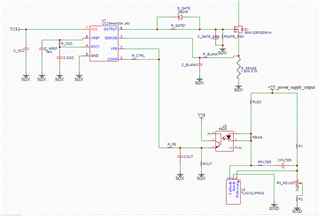

我构建了一个简单的 UC2844测试电路、如下所示。 请注意、负载是1.8K 电阻器。 我通过连接 COMP、FB 和 CS 引脚强制 PWM 输出为50%、如下所示。 fsw = 62kHz (近似值)。

负载为1.8K 时: 黄色迹线=输出引脚、蓝色迹线= Vcc 引脚。 请注意栅极信号开始处的过冲(或偏移)。 请注意每个栅极脉冲信号变化时 Vcc 上的振铃噪声。

在1.8K 负载和串联 LED 的情况下添加了: 黄色迹线=输出引脚、蓝色迹线= Vcc 引脚。 栅极脉冲的开始有振铃、但过冲(或偏移)似乎减少或消除。 每次栅极脉冲信号变化时、振铃噪声都保持在 Vcc 上。

在1.8K 负载条件下、添加了串联 LED 并且 Vcc 输出电容= 15uF 而不是1uF: 黄色走线=输出引脚、蓝色走线= Vcc 引脚。 通过将 Vcc 的输出电容器更改为15uF、没有明显的改进。

请告诉我您的想法。

Thx。

Jav