主题中讨论的其他器件: TPS65916、 AM5716、 TPS65919-Q1

尊敬的专家:

我们正在设计采用 AM5716和 PMIC TPS65917-Q1的新电路板、之前我们使用的是 TPS65916、但现在不再提供。

我的参考资料是:SLVSCO4D (TPS65917-Q1数据表)和 SLVUAX9E (TPS65919-Q1和 TPS65917-Q1用户指南)。

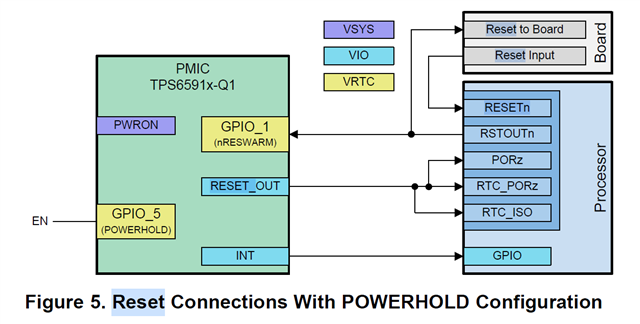

我有图5所示的架构、其中 FPGA 驱动 EN (TPS65917的 POWERHOLD-GPIO_5引脚)和热复位(Sitara 的 RESETn 引脚 E23)。 BOOT=1 (连接到 LDOVRTC_OUT)

根据 SLVUAX9E 第6.3段:"热复位通过将 NRESWARM (GPIO_1)设置为低电平来触发、这会导致执行 OFF2ACT 序列、而不管实际状态(活动、睡眠)如何、并且器件返回或保持活动状态。 [...] 此外、如果 boot=1、那么在蠕虫复位序列期间、RESET_OUT 被置为低电平。 [...] 如果使用 BOOT=1、则必须通过 POWERHOLD (GPIO_5)引脚启用 PMIC。[...]。 如果 POWERHOLD 在 BOOT=1时设置为 GND、则 PMIC 将在热复位序列期间关闭。"

我的问题是:

- 当我驱动 Sitara 的低 RESETn 来驱动 PMIC 的低 NRESWARM (GPIO_1)时、RESET_OUT 不会变为低电平。 ARM15停止工作、我必须关闭并打开电源。

- NRESWARM (GPIO_1)和 POWERHOLD (GPIO_5)都处于低电平 ARM15停止工作、并且我必须断电和通电。

借助 PMIC TPS65916、我必须驱动低电平、然后驱动高电平 NRESWARM 和 POWERHOLD、以便使 RESET_OUT 为低电平并重新启动系统。

我的三个目标是:

- 打开系统->确定这可以正常工作

- 重新启动 Sitara 更改引导顺序-> KO 和 Sitara 冻结(TPS65916正常)

- 关闭系统-> KO

可以帮帮我吗?

此致

弗朗西斯科