大家好、团队、

连接:Vs=24V、Vdd=5V 来自外部独立电源;OUT1上的负载大约为10mA

断开24V 电源时、VS 引脚应为0V、对吧? 但保持在4.2V、UVLO 不会触发。

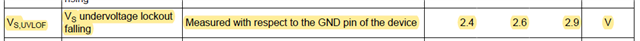

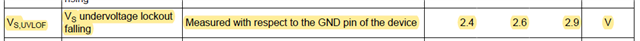

第8页显示了 Vdd 介于3.0V 和3.6V 之间时 VS 的 UVLOF;Vdd=5V 时这些值是什么?

此行为与 EN 引脚的逻辑状态无关。

根据数据表、Vdd 可以为5V。 当施加 Vdd = 5V 时、如何确保 VS = 0V?

如何确保检测到 UVLOF?

谢谢、最诚挚的问候、Hans

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、团队、

连接:Vs=24V、Vdd=5V 来自外部独立电源;OUT1上的负载大约为10mA

断开24V 电源时、VS 引脚应为0V、对吧? 但保持在4.2V、UVLO 不会触发。

第8页显示了 Vdd 介于3.0V 和3.6V 之间时 VS 的 UVLOF;Vdd=5V 时这些值是什么?

此行为与 EN 引脚的逻辑状态无关。

根据数据表、Vdd 可以为5V。 当施加 Vdd = 5V 时、如何确保 VS = 0V?

如何确保检测到 UVLOF?

谢谢、最诚挚的问候、Hans

您好、Hans、

您可以通过为 EN 引脚施加 HI 信号来检查器件是否处于 UVLO 状态、并检查 VOUT 是否与 VS 相同(如果 FET 已导通)。 如果它处于 UVLO 状态、输出应该一直保持在0V。

需要检查的一点是:在本例中、当您在 VS 时观察到4.2V 电压时、VS 是否浮动? 您能否在施加3.3V VDD 时检查 VS 电压是多少?

此外、最好共享您拥有的原理图。

谢谢!

此致、

您好

您好、您好、Yichi、

10k 下拉电阻器无法解决问题。

电位计连接到 VS 时的测量结果表明、需要大约50mA 的电流来触发 UVLO。 电阻为30欧姆、耗散的功率为19W!

同样值得怀疑的是、是否可以通过 Vdd 引脚承载50mA 的高电流。

请告诉我如何解决此问题、我认为这种行为需要反映在数据表中。 可以将 Vdd 限制为3.3V。

谢谢、最诚挚的问候、Hans