大家好、

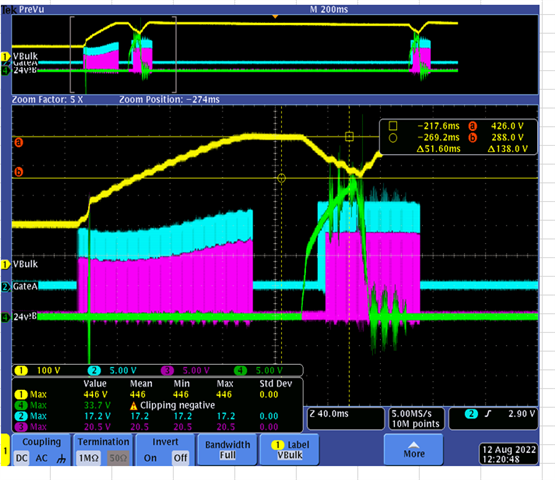

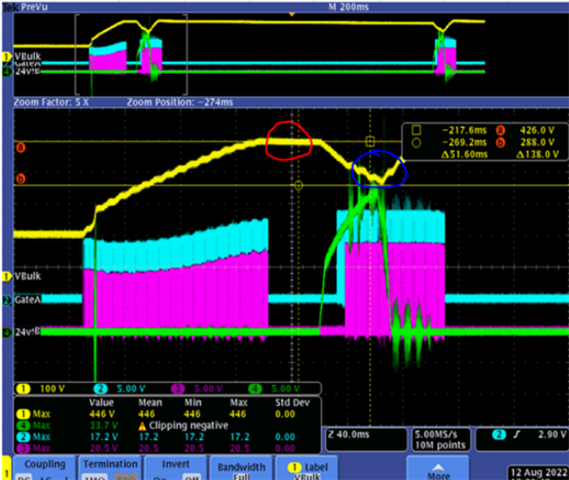

我的客户发现、在更高的功率负载下、PFC 输出会降至288V、导致 LLC 关断、我们怀疑这可能是 OVP、因为输出达到426V、高于 OVP 422V、

我想知道、如果大多数参数都遵循计算器工具、

我们可以采取什么行动来避免这种情况?

BTW、占空比为 95%

Excel 下面是由他们组织的问题,请参阅它以了解更多详细信息。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 Ray:

我想知道为什么我们不能这样做,

我认为只要 Vsense 和 HVsense 的电压与计算器中原来的两个独立分压器的电压完全相同,就可以了, 是否还有其他潜在的风险我会错过这里 ,例如瞬态?

以下是我与当地 AE Adam 讨论的四个结论:

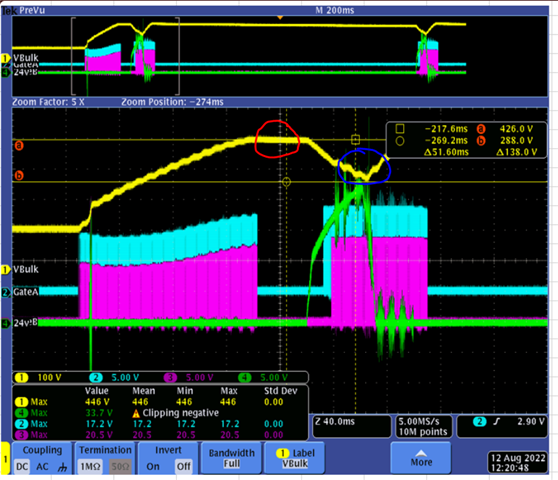

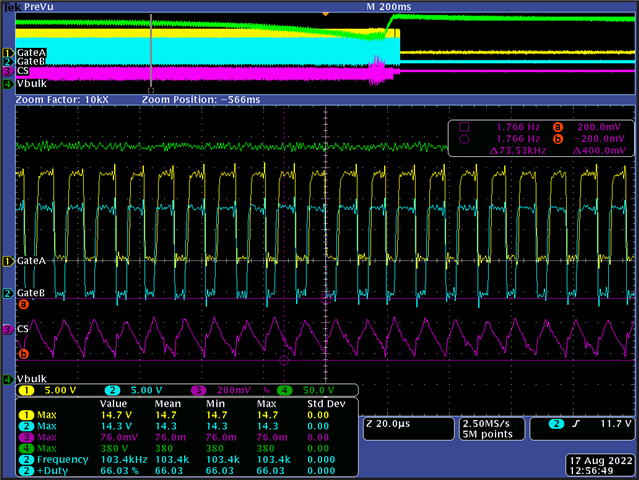

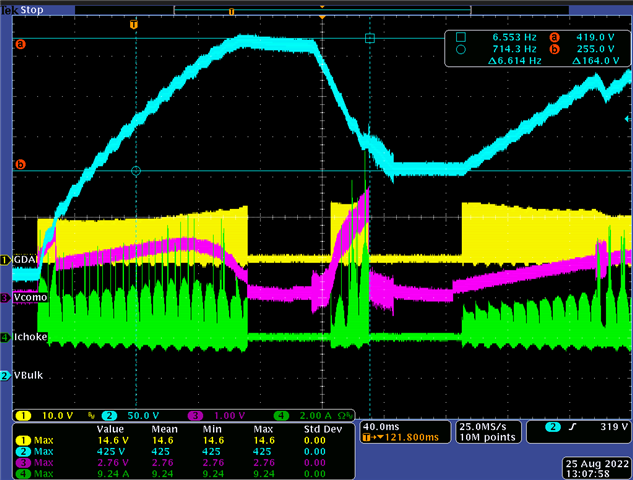

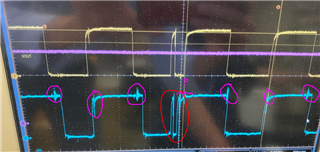

1.红色圆圈是启动过冲期间的 OVP、Adam 建议移除 Vsense 电容 PC410以增加响应、我们还需要移除 PC418吗?

2.对于蓝色圆圈、是由于瞬态响应不足、NXP LLC 具有 UVLO 功能、因此当压降过大时、LLC 将关断。

Adam 建议修改薪酬网络。 对此有任何反馈吗?

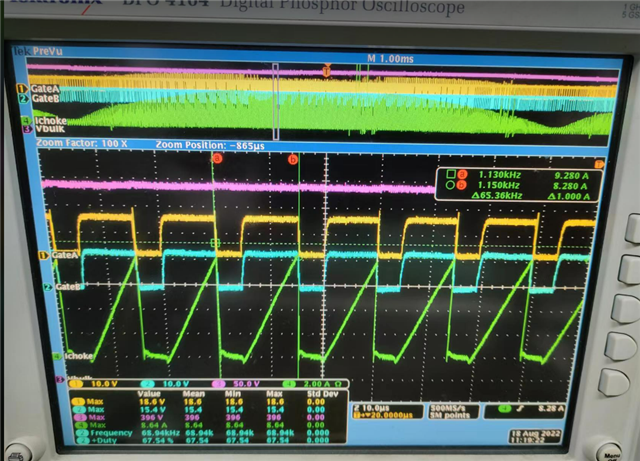

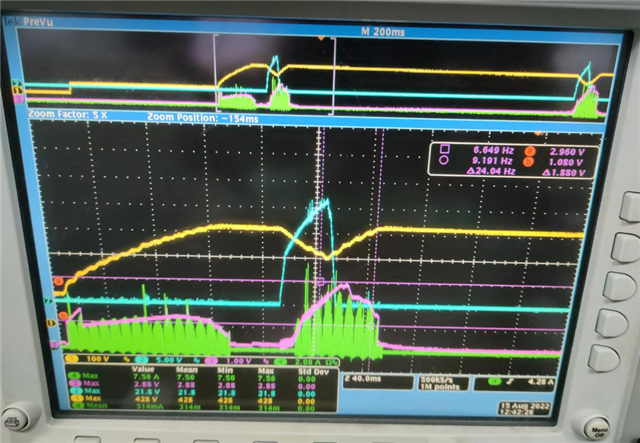

第三种情况是客户缓慢增大负载时、 当输出为360W 时 Vcomp (粉色1)达到5V、

但最大负载实际上设置为500W,这意味着 Vcomp 会超出预期。

有什么想法我们可以解决这个问题的原因和方法吗?

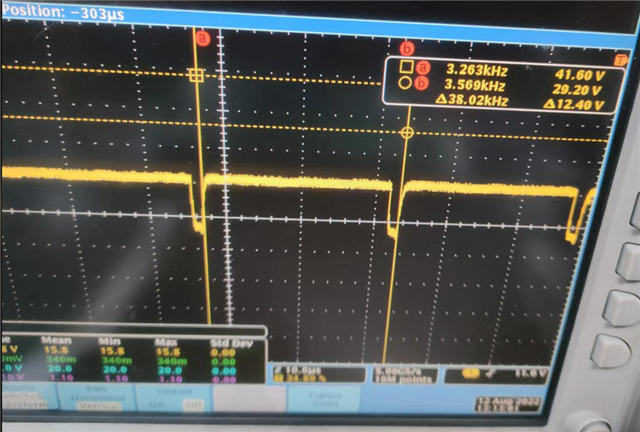

4、 这也很严重, 他们同时发现意外的峰值电流(绿色)和 GDA GBB 脉冲(黄色和蓝色),这是异常的。

Adam 建议在 CS 引脚处增加 RC 滤波器、如果认为有所不同、请告知我、谢谢

请帮您解决以上四个问题、客户现在比较困惑、谢谢

此致、

Fred

您好、Fred、

关于 HVSEN 连接、一般的想法是具有两条独立的过压感测路径、一条从 Vout 到 VSENSE、另一条从 Vout 到 HVSEN。 现在的配置方式是、HVSEN 阈值非常低、因此它永远不会看到4.67V。

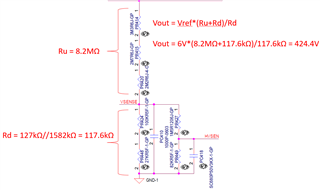

1、如果这与您在另一个 UCC28064A 接线柱中共享的设计相同、我计算 出 VSENSE 到 GND (Rd)的并联电阻为117.56kΩ Ω。 这将导致~424V 的稳压输出、这正是首次示波器捕获时输出的确切位置。 因此、它看起来不是 OV、而是使用所选值进行电压调节。

2. 我认为增加补偿是明智的。 尝试将 PF430提高2倍至4倍(12kΩ μ s 至48kΩ μ s)以改善响应。

3、这意味着设计的功率为500W。 将电流感应电阻器与您看到的差值成正比(~ 40%)

4.看来 MOSFET 在关闭后被触发打开,您正在获得 反向恢复。 这可能是由于 ZCD 信号反弹所致。 尝试将 PR401和{R433增加2倍- 4倍、以查看这是否解决了问题。 您可以首先使用上述波形探测 ZCDx 以进行确认、然后增大电阻器、直到条件得到解决。 然后、您可以微调 R-C 以获得 ZDCx 上所需的延迟。

此致、

射线

尊敬的 Ray:

非常感谢您的反馈。

1.很抱歉、我没有更新最新值、因为他们已经更改了它、

PR448+PR424=150K

PR427=390K

PR449=470K、 这将提供大约392V 的输出电压、正如您可以自己计算的那样。

150k ||(390K+470)=127K

6Vx (8.2M+127K)/127K=392V、因此应该可以

如何通过对 PC410和 PC418的反馈来防止出现大过冲?

3.

您是否会解释 降低 Rsense 有何帮助?

我认为这只是针对 OCP。 Vcomp 应与 Vinac 或 Rset 相关?

您是否认为问题4可能是导致这种情况的根本原因?

4.

我知道 ZCD 的下降可能是由于 DCM 中的谐振恢复、但也可能是由 OCP 引起的。

执行此图中的 GDA 和 GDB 看起来是 OCP、因为它们同时关闭和打开。

我们仍然怀疑 CS 引脚(本图中的粉色引脚)可能会发生耦合并被触发的风险 、即使此图中的 CS 引脚尚未达到 -0.2V... 但我们不知道实际的 CS 信号

告诉我您的反馈?

BTW、 前一张图片中的粉色信号是 ZCD、以防您不知道。

您好、Fred、

1A。 您的更新值对于392V 有意义。 然而、HVSEN = VSENSE * 470/(390+470)= 0.547VSENSE。 当 VSENSE 达到6.67V 的 HIGH_OV 时、HVSEN = 0.547*6.67 = 3.68V、该值仍低于4.87V HVSEN_OV 阈值。

1b。 移除 PC410和 PC418应改善响应(但可能会使其易受噪声影响)。 我认为、按照建议增加 PR430对于加快响应时间非常重要。

3.我怀疑它 在达到所需的最大功率水平之前会达到电流限制

4.当 OCP 被命中时、GDX 信号将以同相方式工作。 这似乎是在每个周期触发 OCP 的情况。 CS 具有带宽限制、因此、如果超过200mV、则很难说。 您可以尝试改进 CS 上的滤波(如 Adam 所述)、但我也会降低 RSENSE 值。

如果情况仍然无法按预期工作、则查看电感器电流会很有帮助。

将来当您共享波形时、还请指明功率级别(或输出电流)和 Vcomp 值

此致、

射线

尊敬的 Ray:

1 a。好的、谢谢、但 HVSEN_OV 应该 比 HIGH_OV 高、所以我认为这 不是根本原因、但是的、我会告诉他们增加到接近4.87V

1 b、他们说 GDA 引脚在将 PR430更改为20K 后立即损坏、这是奇怪的、这是可能的吗?

3.因此,在 OCP 事件期间 Vcomp 将为5V,对吧?

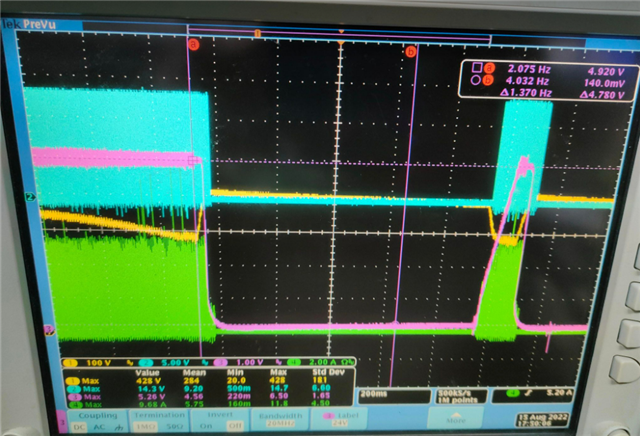

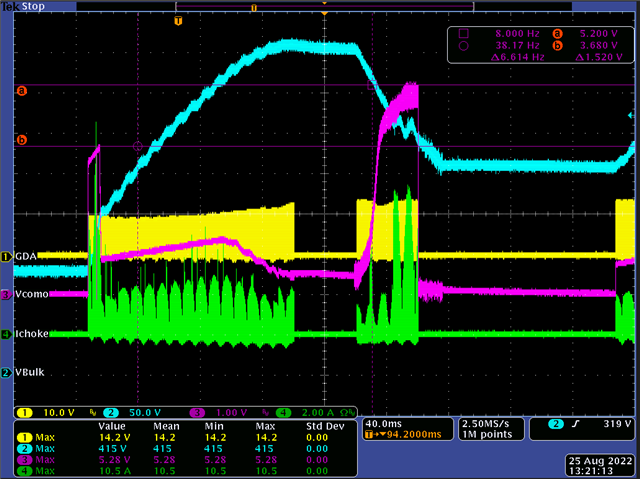

上一张图片是24V/15A、您可以看到输出下降、

在将 Rsense 从0.01降低到0.005之后, PFC 现在可以达到500W (24V/21A,如下所示) ,而不会出现任何压降。

但是、仍然存在同相问题(黄色和蓝色)、这是 OCP 符号、

我们是否应该继续降低 Rsense? 或者是否存在任何其他潜在 风险?

此致、

Fred

1A。 这听起来更合理、可以调整该值、以便能够同时利用 HVSEN_OV 和 HIGH_OV。 我仍然不知道为什么它这样连接、因为它会使事情复杂化并在 VSENSE 上产生额外的电容。

1b。 这并不意味着 GDA 已损坏、尤其是在这种变化下。 MOSFET 的栅极更有可能损坏(防止 GDA 开关)。 不过、除非它导致不稳定的电流信号、否则变化不会实现这一点。

3.在 OCP 期间、您将无法达到所需的输出、因此误差放大器会将 Vcomp 驱动至上限。

4.很高兴听到他们现在达到了全功率级别。 0.005Ω μ A 表示~0.005Ω 0.166V/μ s = 33A 的峰值电流、对于本设计而言、这似乎很高。 您能否确认电流是否达到如此高的水平?

射线

1A。 我理解您的困惑、他们这样做的原因是他们必须通过 ERP Lot 5、这非常关注超轻负载效率、因此我们需要集成两个分频电阻器来传递功耗。

1b。 可能将 PR430更改为20K 会使相位裕度过低、因此会发生振荡... 我让他们尝试降低...

3. 明白了, 因为如果两个 DRV 同相,我们可以正常提供最大功率,对吧?

4、 是的、24V 输出期间的总 E 负载灌电流为500W、 但图中绿色信号中显示的电流看起来正常、

我想可能是 CS 引脚耦合或一些未知干扰、我将向您发送布局、供您明天检查。

只需将 Rsense 短接以检查这是否有帮助? 还是太危险了?

感谢你的帮助

Fred

您好、Fred、

关于#4:我不确定 FET 额定电流是多少,但更谨慎的步骤 是 再降低 Rsense。 流经 Rsense 的电流在两个输出级之间共享、因此您可以进一步降低它。

您可以短接 Rsense、但有损坏 MOSFET 的风险。 如果您可以容忍可能损坏一 个电路板上的组件、如果降低 Rsense 的值无法使您更接近解决方案、则可能有助于进行此调试。

PC406是否紧邻 UCC28064A 上的 CS 引脚? 您可以尝试将其降低至1nF

射线

尊敬的 Ray:

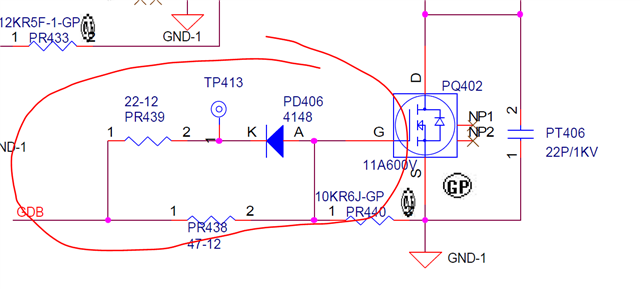

1b。 您是否会检查原理图或布局中的错误、以了解 GDX 引脚为何很容易损坏?

我怀疑可能是寄生振铃?

2.您是否知道软启动期间为什么会有 OVP (红圈)? 我知道在软启动期间应该存在过冲、

但 为什么它只是上升而不是稳定至390V

我认为应该增加 RC 滤波器、以滤除 CS 上的高频率噪声、

您是否会解释为什么要减少它?

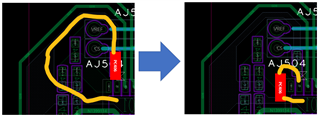

我已经上传了布局、有很多奇怪的东西无法解释、如果有什么奇怪的东西、您是否会检查布局、例如为什么 CS 引脚始终有 OCP

尊敬的 Ray:

以上问题可能是由于 ZCD 阈值太低,我现在知道根本原因。

但您能否在四天前回答前面的问题? 我们 仍然需要您提供这些答案来排除某些原因。

我们已经等了四天的时间来审查您的布局,您能否至少评论一下布局,尤其是电流感?

我不认为 LLC 是所有这些问题的关键、因为如果输出为390V 稳定、LLC 应该是可以的。

但是、我们知道、在稳态期间仍会出现很多问题。 因此、除非 我们给客户足够的理由、否则我不认为客户会购买。

您好、Fred、

关于您的问题:

我有几个问题:

如果您已经验证了补偿组件、但仍然存在启动 OV 问题:

射线

尊敬的 Ray:

该板位于客户的实验室中、幸运的是它现在正在发送到 TI 的实验室。

答案:

对于启动 OVP、请参阅下面的

Vcomp 不是5V、因此我想在启动方案期间没有 OCP、

过冲可能过大、达到428V、并卡在 OVP 和 Vcomp 放电处、直到 LLC 电压上升期间的压降

粉红色是 Vcomp、黄色是 PFC 输出、蓝色是 LLC 输出、绿色是电流

此外,我们还组织了目前为止的所有问题,您可以将其视为版本,而不会在开头进行任何更改。

请帮助检查

e2e.ti.com/.../1581.Copy-of-Interleave-500W-PFC-issue-Summary-20220824.xlsx

您好、Fred、

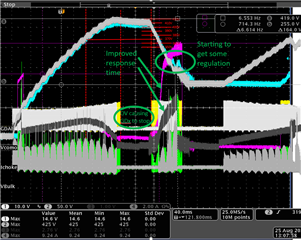

波形确实有帮助。 我可以清楚地看到环路响应太慢。 我建议您重新尝试提高 PR430以加快响应速度的实验。 我建议您安装一个 μ 27kΩ 并重新收集相同的波形。

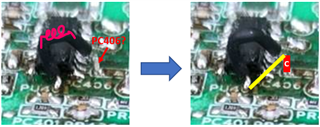

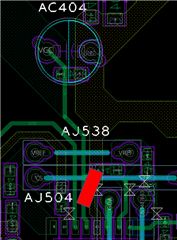

关于 CS 引脚布局、我确实看到了一个可能会有所改进的地方。 这是您可以在现有电路板上尝试的操作(可能使用0805或1206电容在(不必要)通向 BRST 的宽迹线上进行桥接)。 您可以看到、进入 PC406的接地可以缩短得多。 此外、它目前正在运行噪声较大的边 GDB。 我建议采用新布局:

如果您可以在现有电路板上模仿此更改、请复制此早期示波器捕获以查看 CS 上的噪声是否降低或消除。 此外、如果噪声从 GDB 耦合进来、较大的电容器会使这种情况变得更糟、而不是更好。

布局方面还有其他建议、但我想重点介绍导致这些当前问题的原因、因为您无法调节这些问题。

此致、

射线

您好、Fred、

我将与您分享我对该板问题的看法、以便您更深入地了解我的观察结果和问题...

我相信你至少要解决两个问题。 可能还有其他问题、但在我们解决这两个问题之前、很难区分其他问题:

电压环路响应缓慢、导致示波器捕获(使用 Vcomp)演示问题、导致 OV、重新启动、OV 等。

2. CS 引脚上的噪声导致 MOSFET 在 不应导通时导通。 这将导致不可预知的运行状态并可能损坏电路板上的组件。

对于#1、通过增大 Rz (PR430)、您实际上可以加快环路的响应速度、而不是降低其速度。 Vcomp 上升速度更快、对 VSENSE 的响应更严格、如果设置正确、不 会导致 错误的 OV。 关于客户报告的由于增加该电阻器而对 GDA 造成的损坏、我不能认为这样做会损坏 GDA 的任何原因。 但是、我建议您在进行此更改后首次加电时连接一个示波器、以便在发生损坏时将其捕获并进行分析。

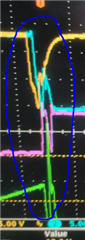

对于#2、我最初认为它与 ZCDx 信号反弹有关。 在查看所有波形后、看起来像其他一些东西、会导致 MOSFET 突然导通、从而产生 电流尖峰。 脉冲非常快(如上面圈出的图像所示)、以至于看起来是感应噪声。 CS 滤波不是噪声源、但如果噪声由包含 CS 电容器的电路板区域及其接地路径拾取、 那么电容器越大、噪声耦合就越大。 通过 调整电容器及其 GND 路径、您可以证明(或消除)这是 CS 和 GDB 之间噪声交叉耦合的原因。

但愿这对您有所帮助。

射线

尊敬的 Ray:

再次感谢您的回复。

但我认为这个 问题与同相问题更相关、而不是启动问题、因此我将要求他们在400W~500W 期间检查 GDX 同相。

同意?

正如我在 GDB 变为 27K 一段时间后再次损坏之前所说的那样。

我可以看到 Vcomp 足够高、这意味着 Ton 足够高但仍然下降、这是否意味着 LLC 启动会吸收 PFC 无法承受的意外电流? BTW、它们使用 NXP LLC

感谢您进行更改。

是的、我尝试使用 CS 电容器解决的问题 与 B 相位内问题和错误触发有关。就实际修改而言、情况不清楚、 但看起来、电容器已移至 AGND 焊盘并重新接线至 CS。 如果这是他们所做的、我会要求他们缩短从电容器到器件引脚的导线。 较短的总线线路更好:

关于启动到 OV、我们 通过使 COMP 更快响应取得了一些进展;它不是完美的、而是更好的。 您现在似乎 需要增加导通时间以获得更大的可用功率、尤其是在 LLC 打开时。 您最终 可能还需要 更多的输出电容、但我认为首先要尝试的是增加导通时间。 您可以通过降低 Rset 来实现该目的。 如果您开始降低25%、那么从165kΩ μ W 降低到124k。 这将按比例增加平均电流。 我不知道 MOSFET 或电感器的额定值是多少、因此您可能需要调整 Rsense 来保护它们。

您的电感器值和电流额定值是多少? 您使用的是什么 MOSFET?

请在更改 Rtset 后共享类似的波形。

谢谢、

射线

尊敬的 Ray:

非常感谢、

因为如果是 OCP、Vcomp 应该是5V、对吧? 如果我错了、请纠正我的问题

更新了 MOS spece2e.ti.com/.../TSM60NC165CI_5F00_A2104_2B002800_update_2900_.pdf

您好、Fred、

就修改而言、我不会对电容的放置位置产生任何问题。 更改的原因有两个:1。 使 CS 滤波器路径远离噪声 GDB 和2. 缩短滤波器路径长度。 他们所做的事情解决了第一个问题(虽然是一个大环路、但 他们形成 了可能会拾取噪声的天线)。 缩短导线将解决第二个问题。

我认为不会发生 OC、否则栅极信号将停止。 在这种情况下、 由于 OV、它们显然正在关闭。

肯定会有改进。 您可以看到负载阶跃响应时间得到改善:

COMP 现在能够 足够快地要求全功率。 我们只需要通过增加导通时间来增加可用的功率。

射线

尊敬的 Ray:

感谢您的解释、

但是、正如我说过的、由于未知原因、他们很容易在更快的响应下损坏了 GDX、

由于样片和电路板数量有限、他们害怕继续、直到我们能够解决这个损坏问题、

我知道您说过、您不确定原因、

但是、只是想知道我们能否通过添加二极管来钳制负电压(GDX 处的阳极)来解决这个问题?

由于 负振铃电压超过绝对规格、这是很可能的。

每个 GDX 引脚上的二极管钳位可用于钳制任何瞬态 电压。 建议使用肖特基二极管、因为它具有低 Vf。 它需要恰好位于器件引脚处才能生效。

即使触发 OCP、Vcomp 也可以达到5V、这完全取决于误差放大器的信号。

我想重申我的建议、即将 PC406降低到至少10nF (并且 PR410 = 100Ω μ F)、以便 CS 块能够足够快地做出反应、从而保护 MOSFET。 既然我们增加了导通时间、那么这种保护就更加重要了。

射线

尊敬的 Ray:

在 Adam 和我将 CS RC 滤波器的电阻器(PR410)移至靠近 IC (如下所示)的位置后、

OCP 同相问题得到解决。 似乎原始跳线与噪声耦合。

我们将继续讨论启动问题、关于此问题、我们将要求客户增加软启动时间、

由于这可能是我们必须增加如此多的补偿和准时赶上进度的原因、这最终与 Excel 计算器完全不同、

您是否认为这是 LLC 软启动灌电流过大所致?

该同相脉冲是否会导致硬开关、从而导致较大的负电压?

由于 Adam 和我认为这可能是导致 GDX 损坏的原因。 您可以看到测量结果,GDB 甚至达到-4.2V...

如果 您也同意、请告诉我这会导致负电压的原因

您好、Fred、

这是巨大的进步。 做得好! 这似乎解决 了噪声耦合到 CS 的主要问题

关于增加软启动时间、是的、这将允许 PFC 输出提供所需的功率。 如果这无法完全解决问题、您 可能仍需要增加导通时间和/或 PFC 输出电容。

您可以观察 到、当下降沿同时发生时、这些脉冲会产生负尖峰。 我不明白为什么示波器报告-4.2V、但我可以看到至少-1.5V (但时间很短)。 当然、如果多次重复或更加明显、则可能会导致组件损坏。

此致、

射线

尊敬的 Ray:

我已尝试在明天将 Rcomp 提高到20K,并将 Rtest 降低到 124k, 在没有任何负载的情况下加电。

很遗憾、就像客户说的那样。 GDX 损坏、VCC 看起来也是如此。

我们无法继续我们计划的解决方案、除非我们能够首先解决此问题、

Adam 说,这是由于接地回路过长,导致快速关断期间产生电感和负电压。

但我只是不明白为什么这种变化会导致快速关闭。 为什么原始补偿不会发生这种情况?

对于我们昨天讨论的情况、

当 OCP 触发时、GDX 为何会受到负值的影响?

如果答案与上述相同,您可以同时回答这两个问题

如果有解决方案,就更好了。

谢谢

现在我看到了大负尖峰(-4.2V)、它就在零时间轴上(它藏在线上)。

我不认为是 OCP 导致 GDX 受到影响。 这些尖峰可能是 由 GDX 路径中的杂散电感以及 GND 引起的。 gdb 特别长、因此更容易受到影响。

您知道该噪声来自哪里吗? CS 滤波的更改是否仍然存在?

它显示在 GDB 中、我想知道它可能还有什么。 它几乎与栅极驱动脉冲同步、但不完全同步。 我仔细看了看,它不是 GDA 馈送到 GDB (或其他方式),所以它来自其他地方。 几乎是拍频分量。 来自 LLC?

射线

您好、Fred、

很抱歉造成混淆。 我 强调电源接地的原因 是参考 我圈出的噪声脉冲。

是的、对于 GDX 变为负值的情况、您突出显示的接地环路是纠正此问题的好选择。

您可以尝试在引脚附近添加一个1uF 电容器、这样可以防止大部分负过冲。 如果这不起作用、您可以在此处放置一个大于15V 的肖特基二极管以进行保护(GND 上的阴极、GDX 上的阳极)。 但是、如果布局正确、则不需要这样做。

下一个电路板、我建议他们遵循 布局建议: https://www.ti.com/lit/pdf/slua959

射线