Thread 中讨论的其他器件: TL431

尊敬的所有人:

在我的项目中、我们将测试输出电路上具有3V3和2、5A 的电源。

n´t、电路没有切换、我们不知道问题是什么、下面是测试点和测量结果的图片。 技术支持能为我们提供帮助吗?

e2e.ti.com/.../TestPointsPowerSupply.pdf

非常感谢。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的所有人:

在我的项目中、我们将测试输出电路上具有3V3和2、5A 的电源。

n´t、电路没有切换、我们不知道问题是什么、下面是测试点和测量结果的图片。 技术支持能为我们提供帮助吗?

e2e.ti.com/.../TestPointsPowerSupply.pdf

非常感谢。

您好!

我查看了您的波形、看起来 VDD 在 VDDon 和 VDDoff 之间循环。 这表示由于故障、设计未启动。

以下应用手册讨论了初级侧故障检测的工作原理以及此技术最常见的问题以及如何解决这些问题。 UCC28740采用此故障传感技术、本应用手册应可帮助您解决问题。

https://www.ti.com/lit/pdf/sluaac5

此致、

您好!

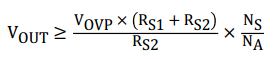

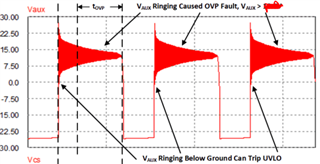

问题1:使用此模块  ,我的 RS1=59K 和 RS2=681k,NS/NA=0.375,因为在我的项目中,我设计的电路在输出电压(VOUT)中使用3V3。 然后、使用该值电阻器、我将 Vout>=3、21V。 在这种情况 下、根据下图、我的转换器设计为在 VOUT 和 VAUX 大于3、21V 时触发 OVP 故障保护。 此陈述是否正确?

,我的 RS1=59K 和 RS2=681k,NS/NA=0.375,因为在我的项目中,我设计的电路在输出电压(VOUT)中使用3V3。 然后、使用该值电阻器、我将 Vout>=3、21V。 在这种情况 下、根据下图、我的转换器设计为在 VOUT 和 VAUX 大于3、21V 时触发 OVP 故障保护。 此陈述是否正确?

问题2:在开关(永久电源)期间,VDD=VOUT*NS/NA=3.21*NA/Ns=8.56V (由 VAUX 供电)。

该值大于 VDDoff (数据表中为7.75V)。

两个问题都正确吗?

谢谢!

您好!

但我将电源设计为具有3V3输出。

因此、如果我增大 OVP 电压、那么我也会增大输出电压。

但我不想这么做、因为我希望 VOUT 上有3V3。

这毫无意义。

那么、我如何设计一个输出端具有3V3而不具有如此低 OVP 的电源呢?

这毫无意义!

根据这个公式 VDD=VOUT*NS/NA=3.21*NA/Ns=8.56V,VDD 中有8.56,所以它不是那么低。

我承认提交的文件非常混乱。

如何调整 OVP 电平? 您好!

我将 RS2值更改为33k (最后一个值为68.1k)。

nA / nS = 2.667; nS / nA = 0.375;

我的 VOUT>=(4.6/33k)*(59K +33k) 0.375 = 4.81V。 如果 VOUT 连续三次、则反激式转换器关闭

开关周期大于4.81V 触发 OVP 保护。

现在、在 VAUX 上、VAUX = nA/ns*VOUT = 2.667*4.81 = 12.82V。

因此、我仍然遇到这个故障问题。

此计算是否正确?

看起来也不是 OVP 问题。

还有其他我可以尝试的方法吗? 可能会进一步降低 RS 值:使用 RS=10k。

谢谢。

您好!

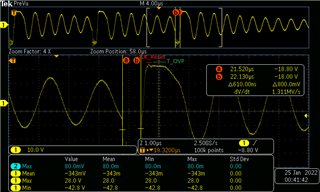

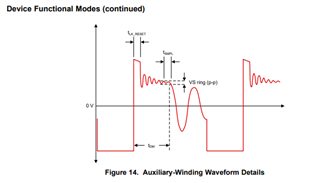

请参见下图。

图1:通道1是 VDD 引脚、通道2是 DRV 引脚。

图2:通道1是 CS 引脚、通道2是 DRV 引脚。

图3:通道1是 VS 引脚(RS2和接地之间)、通道2是 DRV 引脚。

图4:放大图3 -通道1是 VS 引脚(RS2和接地之间)、通道2是 DRV 引脚。

您能在这些图中发现任何异常吗?

图4上的这个电压峰值一直出现在 VS 引脚上。

您认为问题可能是这样吗? 如果是这种问题、我如何解决此问题?

请记住、电路不是在切换、而是设计为在3V3输出电压下工作。

谢谢!

您好!

您需要以更高的分辨率查看关断前的开关波形、以了解关闭的原因。

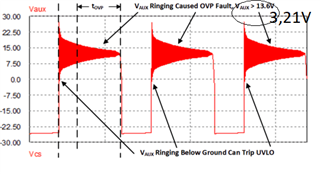

导致问题的辅助绕组噪声。

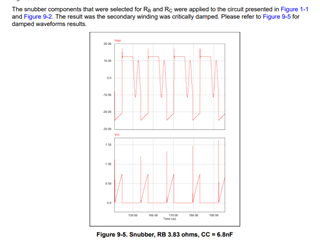

缓冲和 RCD 钳位将清理辅助波形。 应用手册 SLUAAC5详细介绍了如何评估和解决故障问题。

https://www.ti.com/lit/pdf/sluaac5

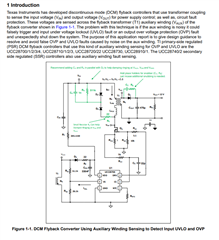

最常见的问题是 AUX 噪声、可通过输出整流器上的 RCD 钳位和缓冲器来解决。 下面以绿色突出显示了这些电路。

此致、

您好!

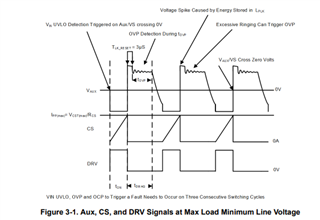

当 UCC28740在最大开关频率下达到 VDDon 时提供三个采样脉冲、如果观察到故障、则会停止开关。 输出上触发、您应该会看到这些脉冲。

请查看我参考的应用手册中的图4-1。 它讨论了三个采样脉冲。

我查看了您的原理图、您使用的是 TVS 钳位而不是 RCD 钳位。 如果您没有在输出整流器上添加缓冲器、 很可能由于 OVP 或 UVLO 而关闭。 应用手册参考详细回顾了这一点。 本应用手册通常可解决98%至99%的这些问题。

此致、

您好!

不确定为什么必须移除电阻器 R6。 从栅极到接地的 R6电阻器为10k 欧姆、只是为了确保 FET 在上电期间保持关断状态。 多年来、设计人员一直在这样做。 这是因为旧器件在 多年前就出现了驱动器高阻抗。 使用该电阻器仍然是一个好做法。

因此、如果您移除 R6并打开保险丝。 FET 的栅极可能已短路至以100%占空比驱动 FET 的电压。 我建议更换熔断电阻器、FET、UCC28740和 CS 电阻器。 此外、检查电路中的所有其他元件、确保它们未损坏。 您应该能够使用欧姆表来实现此目的。

此致、

尊敬的 Mike:

感谢您的反馈。

我有一个新的问题。 现在我们开始:

变压器上的 nA/ns=0.375比率(ns/na=2.667)。

然后,VOUT>=[4.6*(59K+68.1k)/(68.1k)]*0.375= 3.21V。 这是我的电压保护(OVP)。

在这种情况下、当 VOUT 为3.21时、我的 VDD=VOUT*NS/NA=3.21*2.667=8.56V。

VDDoff 最大值为8.15V。

问题1:当输出上有3.21V 电压时、VDD 值非常接近 VDDoff 值。 这可能是一个大问题?

如何解决此问题?

请记住、我将电路投影为在输出上的3V3中运行。

问题2: 在开关期间、VDD 值是否应始终大于 VDDoff 值? 多少钱?

问题3:在图1中、我的 VDDoff=9.2V。 但是、在数据表中、VDDoff=8.15V (典型值为7.75V)。 您会告诉我这方面的什么? 我们有问题吗? 由于 VDD=8.56V、 因此该值低于示波器上显示的值。

谢谢你。

您好!

如果您的输出电压设置为3.3V、则 OVP 跳变点应在大约3.8V 时高出大约15%。 您将需要调整辅助绕组的 VS 电阻分压器。

问题1:

您的 NA/NS 匝数比正确、不适合您的设计。 如果变压器的匝数比为 nA/nS = 2.667、则稳压 VAUX 将为3.3V*2.667 = 8.8V。 我会调整匝数比、使 VDD 标称值约为12V。

VDD/Vout = 12/3.3 = 3.636 = nA/NS

问题2:

反激供电时的 VDD 标称值应大于 VDDoff。 我建议将其设置为12V。

问题3:

VDDoff 的数据阈值正确是一个经测试的参数、 范围应为7.35至8.15V。 不确定您测量9.2V 的原因。

您可能需要对其进行双次检查、以便查看。 放大谷值 并在 VDD 引脚处测量该方向。

您可以在以下链接中找到 Excel 设计工具、也可以使用该工具检查您的设计。

https://www.ti.com/lit/zip/sluc487

此致、

您好!

两者都应保护 FET 免受过压影响。 我发送给您的应用手册显示首选 RCD 电击。 为了安全起见、可以将 TVS 置于 R 和 C 上的 RCD 钳位中。

https://www.ti.com/lit/pdf/sluaac5

此致、

Mike

您好!

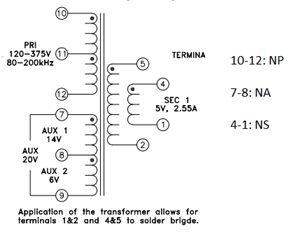

请参见下图。

此图是我们使用的变压器。

选择此变压器时,我们认为 VDD 上的电压应为:VDD=Vin*nA/NP=311*0.114=35V。

当 Vin_rms = 220Vac 时。

但在文档中,您不使用 Vin,而是使用 Vout 来检查 VDD 电压的永久机制:VDD=Vout*nA/Ns=3.3*2.667=8.8V

为什么要使用第二个选项?

此致。 您好、感谢您的反馈。

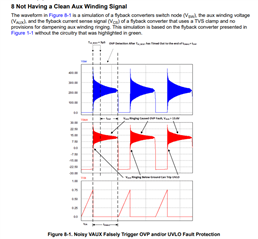

但我有很多问题。 请参见下图。 我们有一个 TLK_Reset 和 T_OVP 表示。

图1;TLK_Reset 和 T_OVP 表示。

图2:您的文档。

我的电路尚未切换。

我将电路设计为在稳态输出下以5V 电压运行。

当存在过压时、输出端将具有5.75V 电压。 变压器的变压比为 nA/ns=2.667;np/na=23.33;

我将电路设计为在稳态输出下以5V 电压运行。

我认为 OVP 保护电压为5.75V。

然后,在永久政权上,VDD=5*2.667=13V。

您的计算器 Excel 文档为我提供 r1=59k 和 r2=27k。

但是、请查看图1。 VAUX 上有 em T_OVP 25V。 SO Vs=25*27k/(59K+27k)=7.85V SO Vs>VS_OVP。 但是、如果我调整 RS2值以解决 OVP 问题、我将更改输出端的保护电压。 问题1:如何以最佳方式继续?

我不明白为什么要测量25V 的 VAUX。

问题2:它应该是 VS 采样=(Vout+VF)*nA/Ns=(5+0.55)*2.667~=15V。 正确吗? 请查看下一个图。

问题3:在图3中、哪个点代表图13中的 VS 采样? 第1点还是第2点?

图3.

您好!

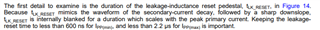

TLK_RESET 为消隐时间、此时您不会检查 OVP。 在 TLK_RESET 超时到采样点后、您将检查 OVP。

请注意 TLK_RESET。 说明了如何根据初级峰值电流电平将 TLK_RESET 设置为600ns 至2.2us。

我在下面发布了信息、但无法改进该决议。 但是、您可以转到数据表以查看相同的信息。

https://www.ti.com/lit/ds/symlink/ucc28740.pdf

如果您的输出电压在 dmag 时间内未上升、则辅助绕组不应达到25V。 可能是变压器连接的极性不正确或匝数比 关闭。 因为 Vout*Na/NP 在 dmag 时间内应大致为 Vaux。 如果 Vout 为零、则在 dmag 时间内 Vaux +处的电压不应为25V。 它应该更接近0伏。

仔细检查变压器匝数比 NP/NS 和 NA/NS 次级、确保它们也正确。

对于您的图3、波形看起来不正确。 谐振环应均匀、并应类似于图13。

下面的波形来自一个正在工作的设计

您的样本波形取值为1。 不确定是什么导致点1和点2之间的波形。 我想知道您的设计中是否有任何分解导致输出电压耗尽。

我建议在此行为期间探测辅助、CS 以及次级绕组和输出电压。 或许这将有助于确定正在分解的内容。

还有一个适用于 UCC28740的评估模块、您可能会发现该模块很有用。 以下链接将带您访问评估模块的用户指南。 用户指南中有一些关键波形、您可以对其进行评估、以查看它们应该是什么样的。 它还提供了设计的原理图和布局。

https://www.ti.com/lit/ug/sluual8/sluual8.pdf

此致、

Mike