主题中讨论的其他器件:TPSI3050

您好!

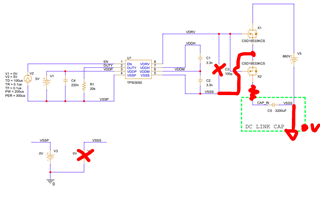

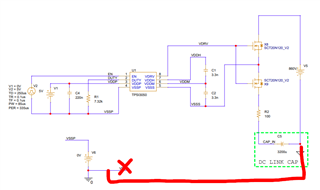

客户写了直流链路预充电原理图。

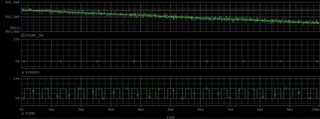

PSPICE 仿真导致错误。

请查看原理图。

2. 请指导我如何改善仿真误差。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

客户写了直流链路预充电原理图。

PSPICE 仿真导致错误。

请查看原理图。

2. 请指导我如何改善仿真误差。

您好、Cho、

感谢您分享! 我们的团队将很高兴在今天下午之前查看原理图。 对于仿真错误、您能否确认这是与您的最后一个线程相同还是不同的错误?

谢谢!

Alex

您好、Cho SR、

非常感谢您提出这些问题。

1-原理图中的以下建议将帮助您的系统达到收敛并按预期运行。

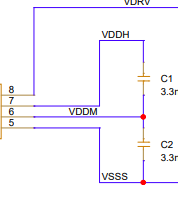

-从 VDRV 上移除负载电容器,因为您已经在为驱动器加载 FET

-将 VSSS 连接到 FET 的源极、因为您需要创建从栅极到源极的潜在差异以驱动 B2B FET。

-让我们在您的链路电容器中添加一个串联电阻器来帮助收敛

让我们为您的电池添加接地、以帮助解决收敛问题

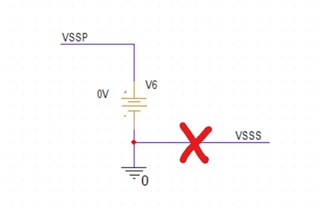

-让我们消除从接地到 VSSS 的电池连接、以消除任何进一步的问题

2 -我注意到您遇到了收敛问题。 我们还可以通过在仿真配置选项中使用自动收敛来放宽收敛变量。

我认为这些建议应该在您的仿真中产生正确的输出、但如果您有任何其他问题、请告诉我。

请告诉我们这是否能解答您的问题。

此致、

弗朗西斯科·劳祖里克。

您好、 Francisco、

客户修改了原理图、并进行了测试。

e2e.ti.com/.../TPSI3050_2D00_Q1_5F00_Schematic_5F00_20211215.pdf

但是、电容器未充电、并且 VDRV 引脚没有信号。

VSS 连接已移除并测试。

结果是相同的。

结果是相同的。

更新的项目文件:

您好、Cho SR、

非常感谢您提供的所有这些信息。

我目前遇到 PSpice 的一些许可问题。 一旦我了解这些问题、我将打开这些文件并提供更详细的反馈。

为了保持调试工作、请执行以下操作:

1 -断开 FET 与驱动器的连接、查看驱动器是否能够在无负载的情况下将 VDRV 切换为高电平和低电平(为负载放置一个10nF)。 我之所以建议这样做、是因为我看到您对 CDIV1和 CDIV2使用的电容非常小。 这些电容值应约为 CG 的10倍。 我注意到 、在您使用的 FET 的数据表中、Qg 大约为45nC、因此您需要增加这些电容器。 我建议对 C1和 C2使用1uf。 如果您看到 VDRV 脉冲、则将其连接到 FET。

2-非常感谢您遵循先前的建议。 我建议消除与 VSSS 的连接、为了加快收敛、我建议在测试这些仿真时将主接地连接到电池接地。

请告诉我们、此回复是否回答了您的问题。

此致、

弗朗西斯科·劳祖里克