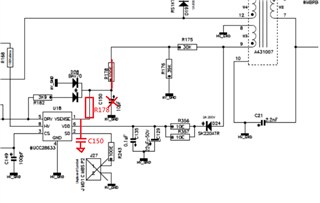

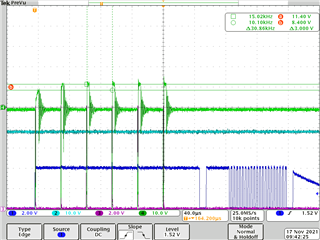

主题中讨论的其他器件: UCC28630

您好!

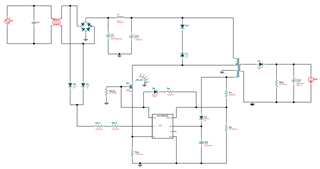

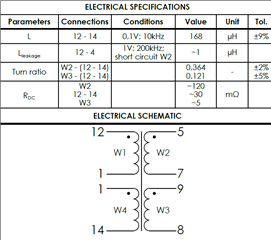

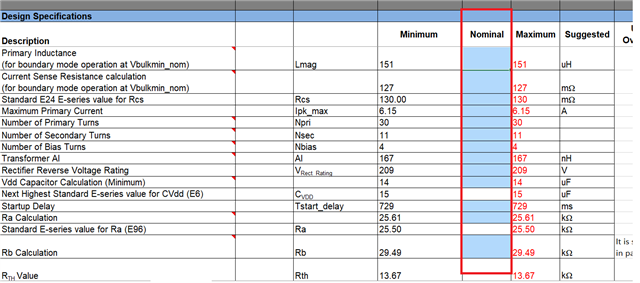

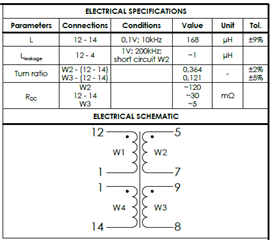

我已经使用 UCC28633制作了反激式原理图。

110V 交流至230V 交流输入、40VDC 2A 输出。

在无负载/轻负载的情况下、我具有以下行为。

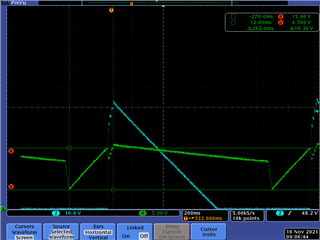

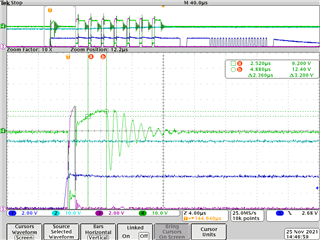

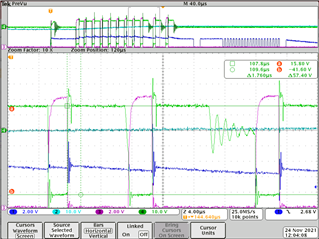

VDD 随 HV 电流源升高。

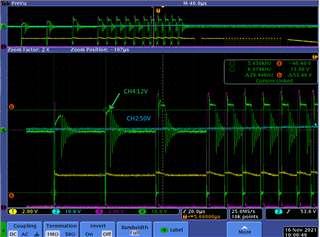

发送线路 UV 校验脉冲。

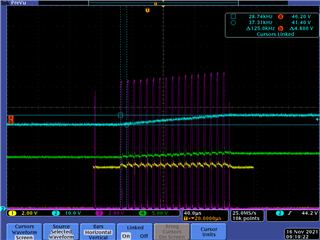

开关以30kHz 的正常 PWM 启动。

VDD 稳定在12V 左右。

开关稳压、直至输出电压约为40V。

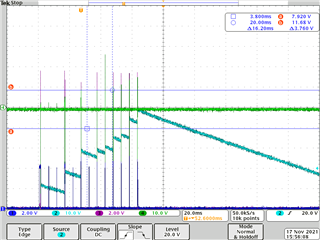

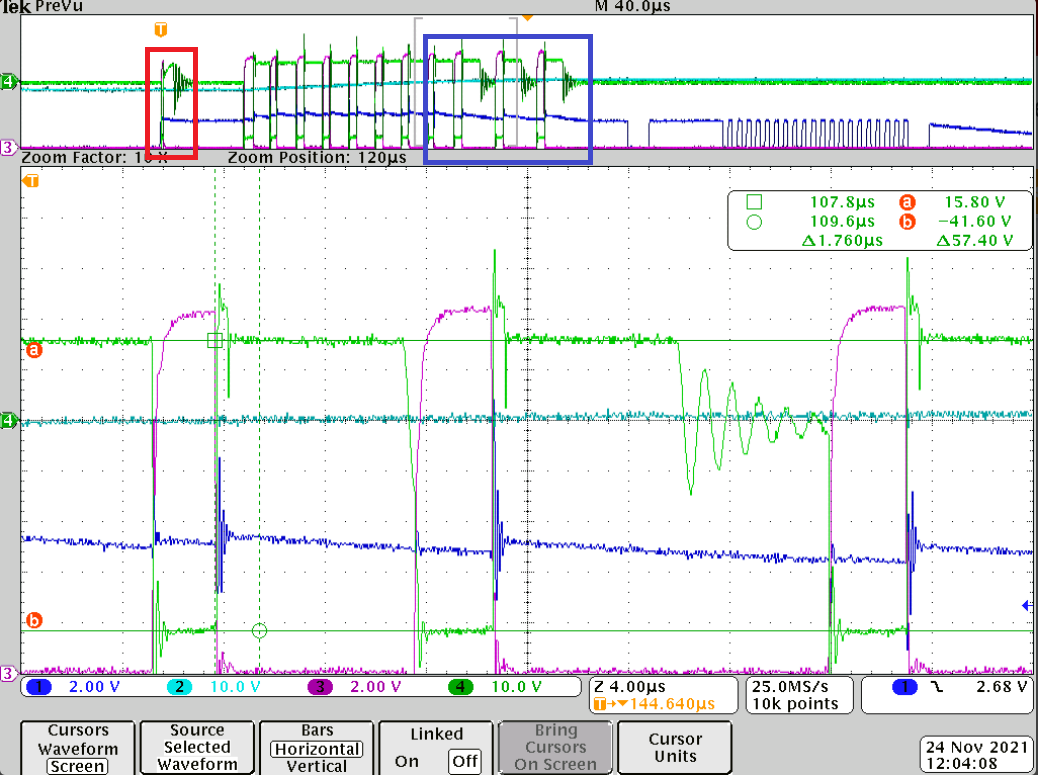

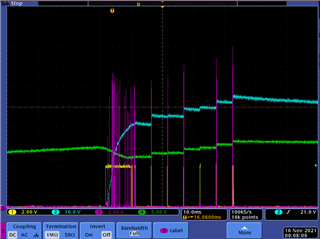

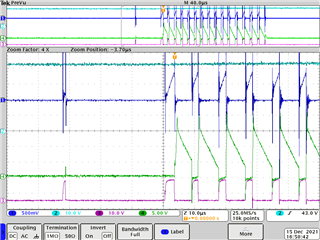

由于轻负载、开关频率达到 大约15kHz 、并进入睡眠模式?

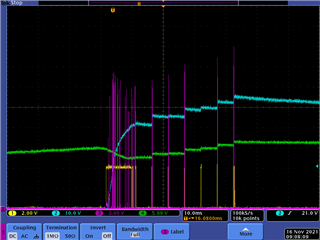

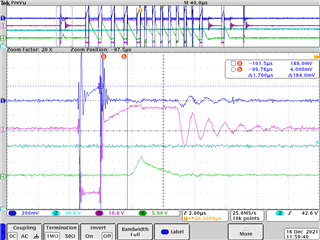

SD 引脚在短时间内变为低电平(20us)。

SD 引脚在下一个开关脉冲时再次变为高电平、并在脉冲之后保持高电平大约45us。

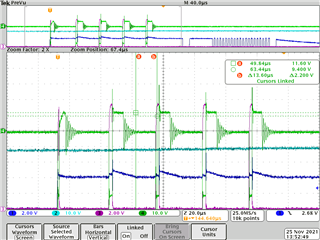

由于开关频率降低、SD 低电平的持续时间会增加。

2个脉冲之间的最后测量时间为365us 或2、7kHz。

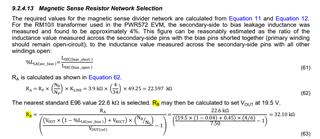

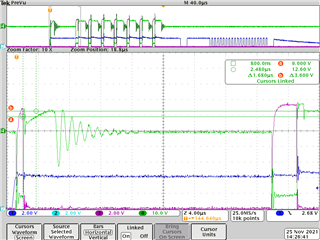

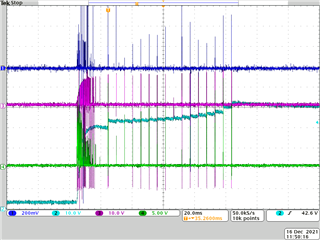

器件进入睡眠模式?

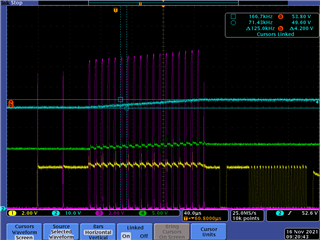

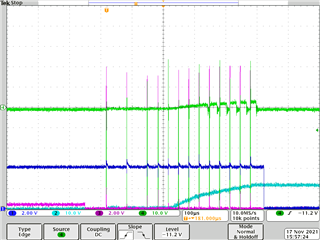

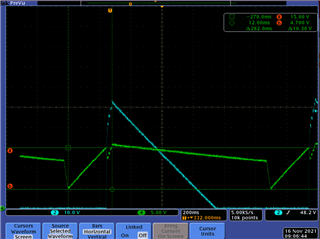

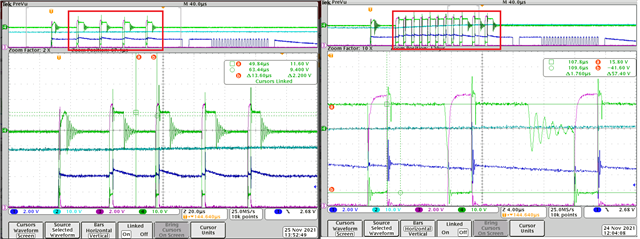

大约5ms (200Hz)后、我看到器件会重新启动它的脉冲。

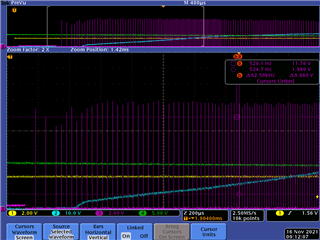

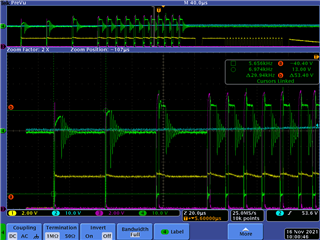

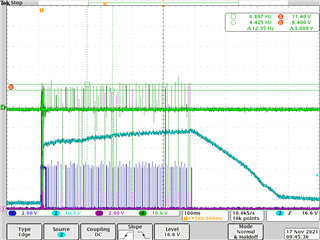

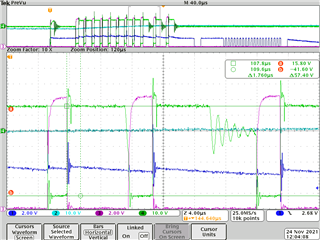

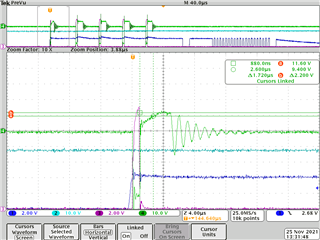

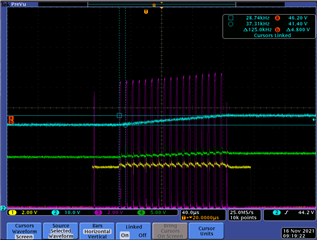

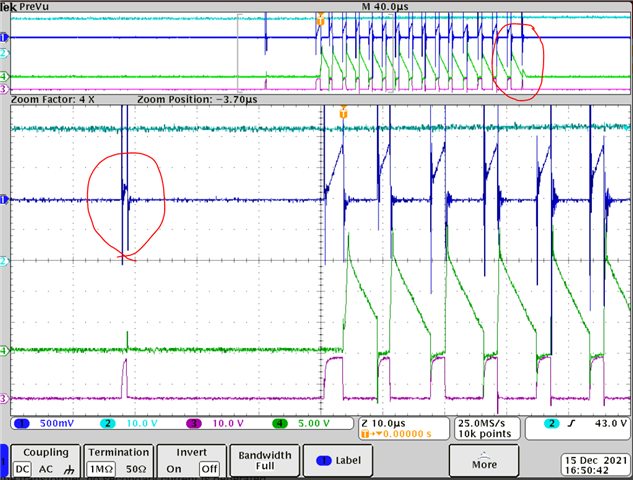

它发送单脉冲(脉冲宽度为600ns)

它等待32us

然后发送17个脉冲、其中 VCS 变为880mV (脉冲宽度约为2us)

这17个脉冲的频率为122kHz

序列以另一个250ns 的短脉冲结束。

每次发生此类序列时、输出电压都会增加。

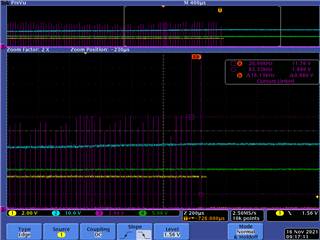

这种情况持续到开关检测到 Vout 为高电平并进入故障模式并自动重启。

如果我用几个方法增加输出、开关将继续工作。

您能不能让我指出优化原理图的拐点、以便它也能在低负载下工作?