主题中讨论的其他器件:UC1846、

我将 UC1846用于反激式转换器

在次级侧短路期间。 COMP 引脚电压下降至零、脉冲在一段时间内停止、然后栅极脉冲出现。

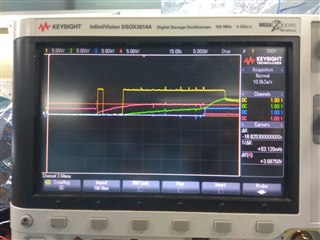

如下图所示、

粉红色是栅极脉冲、当 施加短路时、栅极脉冲停止、而关断引脚为低电平。

当短路完成时、COMP 引脚电压达到高 falling 至零栅极脉冲被停止、无法理解为什么即使没有蓝色的 VOLTGA ON 关断引脚、COMP 引脚也会降至零。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

我将 UC1846用于反激式转换器

在次级侧短路期间。 COMP 引脚电压下降至零、脉冲在一段时间内停止、然后栅极脉冲出现。

如下图所示、

粉红色是栅极脉冲、当 施加短路时、栅极脉冲停止、而关断引脚为低电平。

当短路完成时、COMP 引脚电压达到高 falling 至零栅极脉冲被停止、无法理解为什么即使没有蓝色的 VOLTGA ON 关断引脚、COMP 引脚也会降至零。

您好、Thadisetti、

我可能需要对图片中发生的情况进行额外的解释。

我将尝试解释我从您的解释中了解到的内容。

在反激式转换器中、对 VOUT 施加短路。 UC1846-SP 完全停止栅极脉冲。

在第二张图片中、您说关断引脚上没有电压、但您也说关断引脚为蓝色。

第二张图片中的蓝色信号将变为高电平、这对应于停止的输出脉冲、

对我来说、它看起来就像器件关闭了。

也许您可以标记所有波形以让我有一个更好的想法?

谢谢、

Daniel

Daniel、您好!

蓝色(关断)在延迟后到达,在到达高电压(粉色)后,只有 COMP 引脚电压下降至零之前

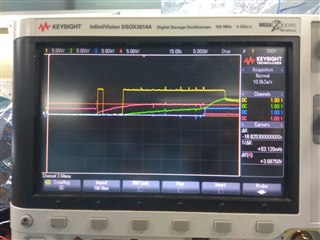

我在这里附加了一个图像

蓝色是 UC1846SP 的 EA+(第5个引脚)它是参考(通过分频器由 ref voltgae 引脚生成的常量)

UC1846的绿色 EA-(第6引脚)感应偏置电压以保持12V 电压、这将与 EA+5引脚蓝色混合。

黄色为 Comp 引脚(第7引脚)误差放大器输出

当我在次级侧短路时、EA-6引脚会下降(如预期的那样为绿色)、并且 COMP 引脚电压会按预期上升、

在这里,我的问题是,

由于未知原因、COMP 引脚(黄色)电压在 EA-引脚(绿色)上升前下降。 我的问题是在光标之间放置。 其中 Ea -(绿色)小于 Ea+(蓝色)、但 COMP 引脚电压下降(黄色)、如图所示、

当在电压大于 EA+(蓝色)的情况下施加外部 EA-引脚(绿色)时、COMP 引脚会降至零、这符合预期。

你(们)好

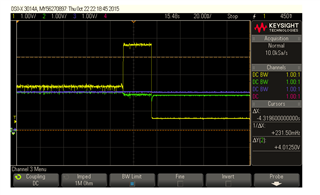

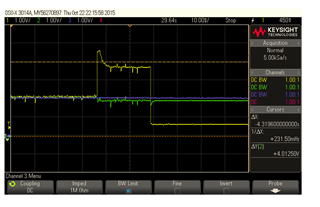

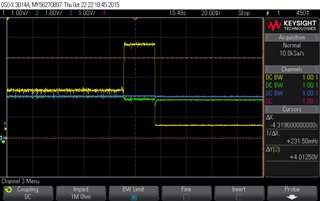

是的,在第一幅图片中,关断将变得很高,因此在第二幅图片中,为了避免噪音干扰,我已将关断引脚短路 (从现在开始,关断电压我们将不再讨论),

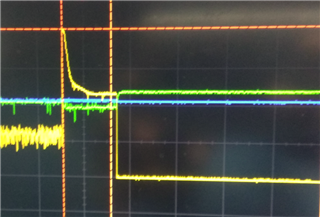

现在、我们将讨论误差放大器引脚 EA+ EA-和 Comp 引脚、如下所示。 蓝色表示 EA+引脚,黄色表示 Comp 引脚,绿色表示 EA-引脚。 当我短路时, EA-(绿色)电压变为低电平,因此 Comp 引脚(黄色达到高电平)。 没关系。

BUR 问题是、如果查看所附的图像、即使 EA-(绿色)与 EA+(蓝色)相比仍然较低、COMP 引脚(黄色)从高电平下降、如所附图所示。

我希望 COMP 引脚(黄色)应该为高电平以保持栅极脉冲。 但 COMP 引脚会下降到某些电压电平(请参见垂直光标之间的)。

由于 COMP 引脚(黄色)从 COMP 引脚上的高电压下降到某些电压,因此我没有获得足够的占空比来在未短接的其他输出上获得输出电压(这是 3输出转换器,一个输出短接的剩余输出应在 一定的最小延迟时间内保持输出电平, 我们注意到的这个逻辑、这里唯一的问题是即使 EA+(蓝色)高于 EA-(绿色)、COMP 引脚(下降)也会下降的原因)

在中

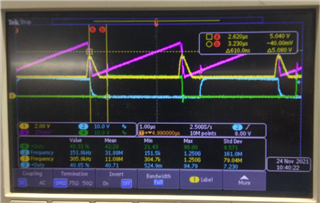

我已将输出行为与 COMP 引脚(黄色)连接在一起

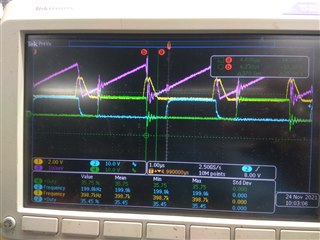

在下图中、粉色是输出(7.3V) I 正在短路。 蓝色表示5V 输出,绿色表示3.3V 输出。 黄色是 COMP 引脚

在下图中、当我短接7.3V 输出线路(粉色)变为低电平、并且 COMP 引脚变为高电平时。 正确、

在此期间、我的 EA-为低 EA+、但 Comp (黄色)未保持高电平。 因此、我在其余输出上没有获得足够的电压(您可以看到下图、输出在这里下降)。 根据我的设计、如果 COMP 引脚在此期间仅保持高电平、我应该根据需要获得输出。

我使用的是2类补偿。

RT CT 使用5.1K 和820pf、并使用2.2nf 和2.38K 的其他组合进行试验、

附加的是占空比波形,最大值为附加的40%。

图1占空比

正如我 之前提到的、我有3个输出、3.8V、5.6V 和7.3V。 我还在相应输出短路期间连接 EA+ EA-和 COMP 引脚的波形。

我仅在7.3V 短路期间出现 COMP 引脚下降问题、而在5.6V 和3.8V 短路期间、COMP 引脚的行为与所连接的情况一样良好。

图示放大器行为 : -+蓝色)(EA-为绿色)针对7.3V 输出短路的补偿黄色

图放大器行为 : -+蓝色(EA-为绿色)针对5.6V 输出短路的补偿黄色

图示放大器行为 : -+蓝色)(EA-为绿色)对于3.8V 输出短路、Comp 为黄色

你(们)好

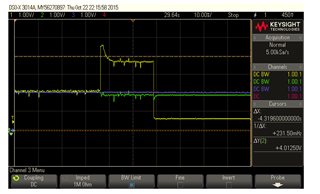

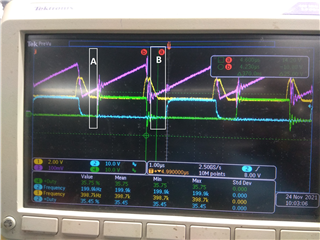

我已经使用 SYNC 和 OUT 引脚进行了检查

所附图像用于同步引脚、CT 和栅极输出、A 和 B

粉色是 CT,黄色是 SYNC,绿色和蓝色是 Gates,我只使用一个,另一个保持打开。

我得到的死区时间为750ns、占空比为35%。

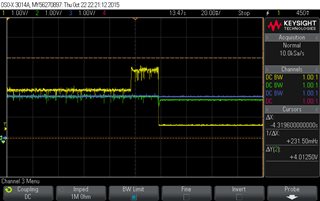

正如我之前所说的、我的主要问题是在7.3V 输出短路期间、COMP 引脚从4.65v 下降到3.3V、但在5.6v 短路时不是这样。

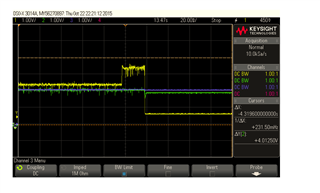

上图在5.6v 短接期间、黄色为 COMP 引脚、绿色为 EA-引脚、蓝色为 EA+引脚、在这种情况下、COMP 引脚处于高电平期间的剩余输出保持稳定。 之后,我们从外部触发关断引脚,使 comp 引脚达到零,这对我来说是可以的。

上图在7.3v 短接期间、黄色是 COMP 引脚、绿色是 EA-引脚、蓝色是 EA+引脚、在这种情况下、剩余输出 下降

您好、Thadisetti、

虽然 COMP 行为很奇怪、但我开始认为它可能是症状、而不是原因。

COMP 在内部变为高电平实际上应该使输出保持导通而不是关闭。

查看我要求的图片:

我已经将两个段标记为 A 和 B 段、想象这两个段处于同一周期。

为了清晰起见、我将这些部分放在了不同的周期中。

B 部分的开头是占空比低、这是有道理的。

SYNC 被强制为高电平将终止输出并启动新周期。

在 Sync 变为低电平之前、您将会在其中切断一些占空比。

似乎还有一个额外的延迟(A 部分)、这是削减最大占空比的原因、这在相当奇怪的情况下。

过去有一些内部延迟引起了问题、但通常是同步信号过长、而 UC1846-SP 在同步后延迟过长。

也就是说、在与旧的 BJT UC 器件同步期间丢失最大占空比是一个非常常见的问题。

我很好奇 A 部分(似乎是由 UC1846-SP 器件引起的延迟)是否与您正在运行的其他测试一同存在。

是否可以在其他电压短路测试中采用相同的情况?

谢谢、

Daniel

你(们)好

我们讨论过的有关同步和占空比波形的哪些图像是在开环条件下拍摄的(即不应用短路、只提供 Vin 并检查占空比和同步)。 我只是向您分享了波形、因为您要求我共享同步波形(在短时间内、我没有捕获同步和占空比)。

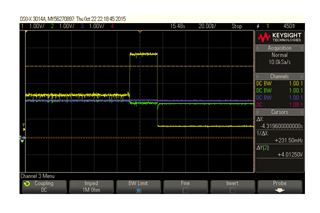

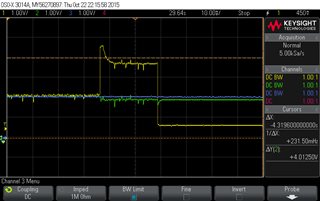

正如您问我的、我在短时间内没有同步波形。 但我在不同的 RT CT 条件下具有波形 RT 10.2K、下面连接了 CT 680PF。

现在、我在不同输出电压下具有 COMP 引脚和 EA+ EA-行为、我已经向您分享了这些行为

并再次连接

上图7.3V 短接期间、COMP 引脚呈黄色下降、EA+蓝色、EA-呈绿色

上图5.6V 短接期间、COMP 引脚在 4.6V 时不会下降、EA+蓝色、EA-为绿色

上图3.3V 短路期间、COMP 引脚未呈黄色下降、EA+蓝色、EA-呈绿色。