请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TPS3431 即使在使用 STM32的 GPIO 引脚在超时(1.6秒)内提供 WDI 脉冲之后、WDO 也会被置为有效(逻辑低电平)。

当 SET1引脚被强制为低电平时、它也被置为有效。

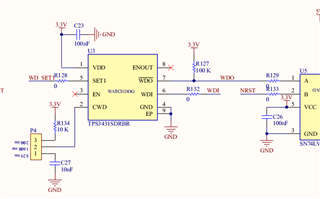

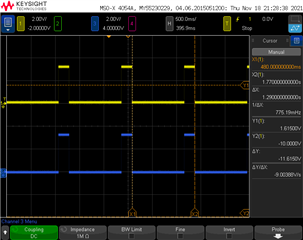

请找到随附的定制电路板原理图和示波器屏幕截图(蓝色=WDI;黄色=WDO)。

启用看门狗的伪代码如下所示:

Set1=1;等待100ms;

WDI=0;

while (1)

{

驱动器 WDI=1;等待200ms;

驱动器 WDI=0;等待1000ms;

}

是否存在对 IC 或我缺失的地方造成部分损坏的可能性。

我有一个要测试的电路板。 此外、当持续保持 SET1 = 1并保持 WDI = 1时、WDO 变为高电平1.6秒、然后变为低电平200 ms、然后再次变为高电平1.6秒 该波形重复出现、因此我认为可能没有发生 IC 故障。