请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TPS1663 你(们)好

我们在设计中使用 TPS16632、客户对 PGOOD 信号有疑问

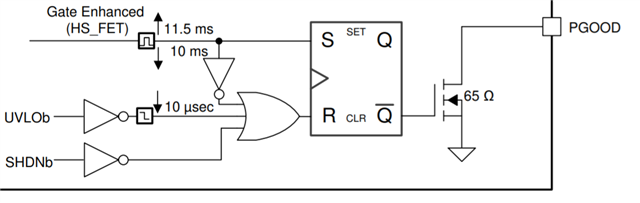

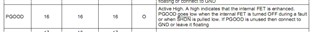

根据数据表9.3.8 (请参考以下图表)、它指出:

'当内部 FET 在故障事件期间或#SHDN 被拉至低电平时、PGOOD 变为低电平'

实际上、没有 关于*故障事件的检测条件/标准的详细说明"(如 OVP 或 OCP 保护? 触发条件为“伏特”或“伏特” 放大器?)

您能帮助提供详细信息吗?

谢谢你

Steven