主题中讨论的其他器件: TPS40211、 TL431

我希望 能够在 TPS40210和 TPS40211器件中使用与 PMP6263类似的电路。 我知道需要对反馈\补偿无源组件进行更改才能使其正常工作、但我找不到任何关于如何为 PMP6263设计开发这些值的参考。 我知道此设计是 围绕 TPS40210内部的700mV 基准进行的 、我还想获取无源组件值、这将允许我使用260mV 基准器件 TPS40211。 感谢你的帮助。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

我希望 能够在 TPS40210和 TPS40211器件中使用与 PMP6263类似的电路。 我知道需要对反馈\补偿无源组件进行更改才能使其正常工作、但我找不到任何关于如何为 PMP6263设计开发这些值的参考。 我知道此设计是 围绕 TPS40210内部的700mV 基准进行的 、我还想获取无源组件值、这将允许我使用260mV 基准器件 TPS40211。 感谢你的帮助。

您好 Natan、

请查看功率级设计器 https://www.ti.com/design-resources/design-tools-simulation/power-stage-designer.html

在选择反激式转换器并输入参数后、环路设计器会帮助优化补偿组件。

此致、

Brigitte

您好、Natan、

我无法确定 PMP6263的设计人员使用了哪种工具、但我假设它是首先使用功率级振铃器进行计算的:

最后针对实际设计进行了优化、通常这是一个很好的做法、可以同时考虑所有寄生因素。

以下是有关补偿的良好文档:

https://www.ti.com/seclit/ml/slup340/slup340.pdf

此致、

Stefan

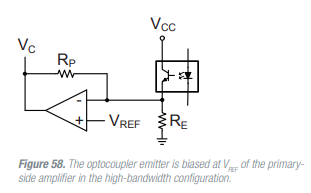

该工具以及文档并未真正指定不同电压基准所需的任何补偿变化。 实际上、文档中的这个图似乎表示任何参考电平应该起作用、因为光耦是通过内部放大器偏置的?

问题的核心在于、目前我们有一个使用 TPS40210的已知工作设计。 我们从电路板上移除器件并放入 TPS40211器件、但我没有进行切换、但我确实从内部 LDO (VBP)获取电压。 对于 TPS40211、除了我在这里应该考虑的基准电平之外、还有其他一些注意事项吗?

Natan、

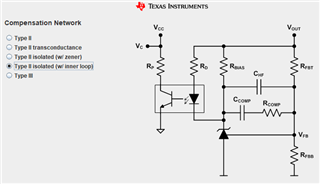

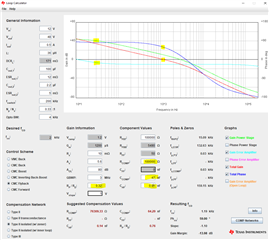

最佳选择是使用 TI 网站上提供的 Power Stage Designer 4.0。 只需单击反激式拓扑、然后选择顶部的环路计算器栏。 然后在左下方为 Comp Network 选择 CCM 反激和 II 型隔离式(带齐纳二极管)。 如果您单击右下角的"COMP Network"按钮、它将向您显示电路。 使用此工具时、请记住以下几点:

- "齐纳二极管"消除了内部环路、通过消除从 Vout 到光耦合器的反馈路径、极大地简化了补偿。

- PMP6263使用此方法、但 TPS40210中也有内部误差放大器、它会增加增益(30k/10K = 3 = 9.5dB 至总环路)。 它还增加了一个 fpole = 30k 和27pF = 200kHz、但这是非常高的并且只用于噪声滤波。

TPS40210和 TPS40211之间的 Vref 差异不应产生影响。 但是、在现有稳定设计上设置输出电压电阻分压器时、只应将较低电阻值更改为(重新)调整输出电压。 这是因为顶部电阻器也是补偿网络的一部分、会影响稳定性、而下部电阻器不会。

此外、在设计功率级时、电流感测电阻值也会对闭环增益产生影响。 电流感应电阻值越低、环路增益越高。 例如、如果其值从0.015欧姆降至0.005欧姆(在现有稳定设计中)、则有效环路增益增加0.015/0.005 = 3X =>+9.5dB。 这会将带宽推高、并可能导致低相位裕度和不稳定。 一个简单的纠正方法是将 Rcomp 降低3X、将 Ccomp 增加3X (这使补偿为零)、并将 CHF (高频率补偿电容)增加3X。

感谢您提供的其他信息、我当时有点卡滞了。 我的设计不完全是 PMP6263、但几乎与 PMP7132完全相同、出于某种原因、已从网站中删除了哪一项? 我所做的就是将 TPS40210与 TPS40211交换。 我没有进行切换、但 VBP 上的读数为8.2V、COMP 上的读数为0.26。 哪些似乎是更有价值的、 您是否有更多的故障排除想法? 此设计已投入生产多年、采用 TPS40210、只是为了能够在目前芯片短缺的情况下获得第二款器件。

尊敬的 John:

我能够附加这些文件。

此致、

Stefan

e2e.ti.com/.../56V_5F00_0.35A-flyback-Mathcad-pdf.pdf

e2e.ti.com/.../Power-Tip-_2300_98-_2D00_-Designing-a-DCM-flyback-converter.pdf

e2e.ti.com/.../PowerTips-Designing-a-CCM-flyback-converter.pdf

Natan、

如果 COMP 电压为0.26V、该电压过低、将阻止 PWM 启动。 它必须高于这个值(假定输出电压为0V)。

我相信您在40211上看到的问题是内部0.26V 基准以及 COMP 和 FB 以及光耦之间的两个电阻器设置的增益造成的。 从 COMP 到光电耦合器(引脚3)的增益为 Vcomp =-Vi*RF/Ri + Vref*(1+RF/Ri)=-Vi*3 + Vref*4。 尝试在 Excel 中绘制此图。 使用40210时、Vref 为0.7V、因此内部 E/A 的增益不同于切换到40211时的增益。 当 Vref=0.7时、电阻器值被设定、这样的话、COMP 输出电压可在0V (零 PWM)至~3V (100% PWM)的范围内摆动、以实现1V 至0V 之间的输入电压(光电引脚3电压)。 如果您更改控制器(Vref = 0.26V)、COMP 电压只能高达1V (不再是3V)、这不足以使 PWM 启动。 请记住、高 COMP 电压=高 PWM。 因此、如果使用40211、请尝试将反馈电阻器从10K 更改为34K。 这将使反馈增益从3增加到~10、并应允许 COMP 电压达到高达~3V 以获得100% PWM。 但是、这种更高的增益还意味着光耦引脚3上的满摆幅电压将从1V 降至0.3V。 我认为这种变化会增加环路增益、因此可能需要重新补偿(在 TL431周围)。 尝试此更改、看看转换器是否开始切换。

| 六 | VR | 射频 | RI | Vcomp | 六 | VR | 射频 | RI | Vcomp | |

| 0 | 0.7. | 10000 | 3320. | 2.81. | 0 | 0.26. | 34000 | 3320. | 2.92 | |

| 0.1. | 0.7. | 10000 | 3320. | 2.51. | 0.1. | 0.26. | 34000 | 3320. | 1.90 | |

| 0.2. | 0.7. | 10000 | 3320. | 2.21. | 0.2. | 0.26. | 34000 | 3320. | 0.87 | |

| 0.3. | 0.7. | 10000 | 3320. | 1.90 | 0.3. | 0.26. | 34000 | 3320. | -0.15. | |

| 0.4. | 0.7. | 10000 | 3320. | 1.60 | ||||||

| 0.5. | 0.7. | 10000 | 3320. | 1.30 | ||||||

| 0.6. | 0.7. | 10000 | 3320. | 1.00 | ||||||

| 0.7. | 0.7. | 10000 | 3320. | 0.70 | ||||||

| 0.8. | 0.7. | 10000 | 3320. | 0.40. | ||||||

| 0.9. | 0.7. | 10000 | 3320. | 0.10 | ||||||

| 1 | 0.7. | 10000 | 3320. | -0.20 |

Natan、

现在可以听到输出电压正在调节的声音。 我不认为光耦合器到 GND 的分辨率值(1K)不应影响增益。

在您的设计中、有一个频率为~15KHz 的 RHPZ、因此您应该将转换器 BW 的预期设置为该最大值的~1/5 您无法获得接近 RHPZ 的稳定 PS。 我会说尝试获得1K-4kHz 带宽、相位裕度大于45度。 RHPZ 频率在最大负载和 Vin 最小时最低、因此请务必在此处进行检查。

在您发布的补偿数据中、我注意到 Rp/Rd 比率在0.032时非常低。 通常、这应尽可能接近1。 假设您可以将其增加到0.32、我附加了一组可能的补偿值。 ~30Hz 处的功率级极点现在与补偿网络(Rcomp 和 Ccomp)的零点对齐。 这对增加~1.5KHz 时的相位裕度(黄色)有很大影响。 这里的 PM 约为60度、这很好。

Natan、

RP/Rd 为 R26 /(R18+R15)、位于光耦的任一侧(请参阅随附的)。 因此、R26确实会影响整个环路增益的增益、但不会影响我之前提到的 TPS4021x 内部 E/A (R17和 R24)的传递函数。

很抱歉、但要使其更加复杂、但 R26和 C25会形成额外的极点(假设 R28 = 0、如 PMP6263中所示)、或 R28非零时的极点-零组合。 下面显示的比较器网络中未包含这些内容、但仍需加以考虑。 R28-C25的解释会变得相当复杂、但简而言之、在使用 Opto 网络时需要进行说明-"使用 Optto (带内部环路)隔离的 II 类"。 遗憾的是、我不知道有什么参考资料可供参考、但下面的链接可能会有所帮助。 C25 - R28 - R26的"目标"是降低内部环路的增益。 由于 R18/R15直接连接到 Vout、因此这是嵌套内部环路。 使用 PMP6263的"齐纳"方法、可以消除内部环路、而无需 R28。 因此、在为 TL431选择补偿值时、齐纳方法可以显著简化补偿。

https://www.eetimes.com/power-tips-compensating-isolated-power-supplies/

如果您想使用 PMP7132的30.9K 和1K 值(Rp/Rd = 0.032)、这是很好的、因为该设计具有很好的稳定性。 一般来说、我经常看到这个比率要小得多、但在本例中、它是有效的。 只需更改 Rcomp 和 Ccomp (来自我之前的帖子)、即可使 BW 处于1KHz 范围内。 请记住、PMP6263使用"隔离式光耦合器/齐纳二极管"补偿网络、而 PMP7132使用"隔离式带内部环路"补偿网络、这就是 Rp/Rd 比率如此不同的原因。 当使用低电压钳位(齐纳)电压时,Rd 值可能会低得多(以及 Rp/Rd 比)。