尊敬的 TI 团队:

我们在 新项目中使用 TPS548D21RVFT 电源稳压器 IC、它将用于为主处理器板上的核心电压(0.8V @ 40A)供电。 这是一款大规模生产的电路板、我们正在对此 电路板进行 EMI/EMC 合规性测试。 因此、考虑到这一点、我们需要在当前设计中注意哪些改进/更正以及所有改进/更正。 另请您查看随附的原理图并提供反馈。

此致、

Vyshnav Krishnan

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 TI 团队:

我们在 新项目中使用 TPS548D21RVFT 电源稳压器 IC、它将用于为主处理器板上的核心电压(0.8V @ 40A)供电。 这是一款大规模生产的电路板、我们正在对此 电路板进行 EMI/EMC 合规性测试。 因此、考虑到这一点、我们需要在当前设计中注意哪些改进/更正以及所有改进/更正。 另请您查看随附的原理图并提供反馈。

此致、

Vyshnav Krishnan

我们不是 EMI/EMC 合规性专家、而 EMI/EMC 合规性在很大程度上取决于直流/直流开关模式电源原理图的外因数、但我们可以在设计注意事项方面提供一些一般指导、以降低传导和辐射噪声。

1) 1)我建议将 VDD 至 GND 滤波电容器从0.1μF μ F 增压到1.0μF μ F、或在 VDD 至 GND 之间添加1.0μF μ F 电容器

这不是 EMI/EMC 合规性问题、而是器件运行问题。

2) 2)我建议包含一个介于22μF μ F 和10nF 之间的中间输入电容值。 虽然10nF 电容器通常有助于抑制开关节点谐振产生的50-200MHz 开关节点振铃频率、但与22μF 电容器并联的10μF Ω 或4.7μF Ω 电容器有助于抑制较低频率噪声。

3) 3)由于铁氧体磁珠(L16)会在输出端的负载瞬态期间阻止 VCC_3V3将动态电流拉入0V8_REG_IN、因此您可能需要考虑一些额外的输入电容、以便在 VOUT 的动态负载期间支持 VIN。 当然、这取决于负载电流的动态特性、因此、如果您使用 L16测试了此设计、则可能不需要这样做。

4)与1.0μF 电压一样、我建议使用一些低值 (0.01μF μ F / 0.1μF μ F)输出电容器、以便为通过电感器传导到输出端的高频噪声提供低阻抗。

5) 5)获得电路板后、我建议按照随附的过程优化缓冲器值: https://e2e.ti.com/blogs_/b/powerhouse/posts/calculate-an-r-c-snubber-in-seven-steps

e2e.ti.com/.../Snubber_5F00_Calculations.xlsx

大多数 EMI/EMC 改进将与布局设计有关。 以下是一些一般性建议:

1) 1)尽量减小开关节点的尺寸。 它应该足够大、以便从 SW 引脚到电感器端子提供导通、但不会更大。 角应在45度而非90度处圆角或倒角。

2) 2)开关节点和输出节点之间的间距不应小于电感器焊盘、以避免增加电感器上的并联电容以及从开关节点到输出电压的高频导通

3) 3)输入和输出电容器应在设计规则允许的尽可能减小寄生电感的情况下、在靠近电容器端子的位置有多个通向接地平面的过孔。

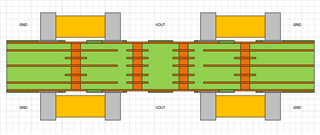

4) 4)将两个电容器端对端放置、并在它们之间放置 VOUT、而在另一侧放置 GND 将提供比并排放置更低的阻抗接地路径。

5) 5)如果电容器可以放置在 PCB 的两侧、 则使用多个 GND 和 VOUT 过孔在顶部和底部镜像该配置将显著降低寄生电感和高频输出传导噪声。 这在 PCB 设计中复制了馈通电容器。