此常见问题 解答介绍了低侧晶体管实现半桥栅极驱动器正常运行所需的最短导通时间

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

此常见问题 解答介绍了低侧晶体管实现半桥栅极驱动器正常运行所需的最短导通时间

栅极驱动器电路最重要的设计参数之一是低侧晶体管的导通时间。 如果导通时间过短或自举电路的 RC 时间常数过大,自举电容器将无法为每个周期充满电,因此自举电压将无法达到电源电压。 自举电压降低将直接导致驱动器输出电压下降。 这会导致 MOSFET 发热、逻辑错误、脉冲缺失以及效率降低。

图1. 自举充电路径

在设计自举电路时、RC 时间常数必须小于低侧晶体管的最短导通时间。 具体而言:

τ= Cboot * Rboot < ton、低侧

但是、为了获得最佳结果、最小导通时间应比时间常数大几倍。 这将确保自举电压保持稳定、从而提高工作裕度、并使自举电路针对非理想情况更加稳健。

图2. 仿真设置

图2显示了用于评估将 RC 时间常数增加到低于低侧 FET 导通时间的效果的 SIMPLIS 原理图。 仿真的运行频率为100kHz、高侧占空比为75%、对应的低侧导通时间为2.5uS。 电阻器 R7和电容器 C2构成自举充电电路。 图3和4中显示的仿真结果是通过电阻器 R7调整时间常数获得的。

图3. VHBHS 用于不同的时间常数

图3显示了自举电容器两端针对不同时间常数的电压。 当时间常数接近并超过低侧晶体管的导通时间(2.5uS)时、电容器每个周期吸收的电荷会减少、并且平均自举电压会下降。

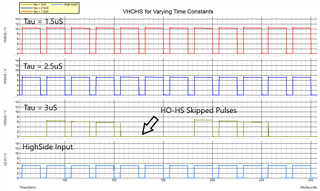

图4. VHOHS 用于不同的时间常数

图4显示了高侧输出和高侧源之间的差分电压。 如图3和4所示、该输出电压直接跟随自举电压。 如果时间常数上升到高于最小导通时间、与时间常数3uS 的情况一样、自举电压将逐渐下降、直到达到5.6V UVLO 下降阈值。 然后、输出被禁用并保持不变、直到自举电压能够充电至高于6.7V UVLO 上升阈值、从而重新启动周期。

图5. 启动期间的 VHBHS

图5显示了器件初始启动期间的自举电压充电情况。 可以看出、自举电路的时间常数越长、电路达到稳态运行所需的时间就越长。

图6. 启动期间的 VHOHS

图6显示了在图5所示的相同充电序列中器件相对于高侧电源的高侧输出。 将图5和6一起评估时、可以看出、较长的充电时间会导致高侧输出在最终达到稳定状态运行之前缺少一些初始运行周期。

参考文献: