请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TPS546D24A 工程人员希望使用 TPS546D24A Avin/PVIN 共模输入电压3.3V 作为 PGD 引脚的上拉源。

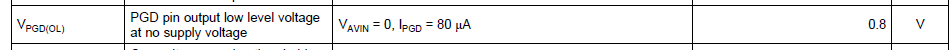

我是否正确地假设,如果我遵循 IPGD 测试条件,则电源正常规格(如下所示的0.8V)将保持到 POR 完成为止。

规格指示 PVIN 已为12V、AVIN 为0V、只是尝试验证在器件上电时不会出现任何 PG 杂散指示。

如果 PGD 引脚为0.8V、这相当于3.465V (最大输入轨电压)范围内的~33.3K 欧姆电阻器、以将电流限制为80uA。

(3.465V-0.8V)/80uA =~33.3K Ω

谢谢、

Brad