您好!

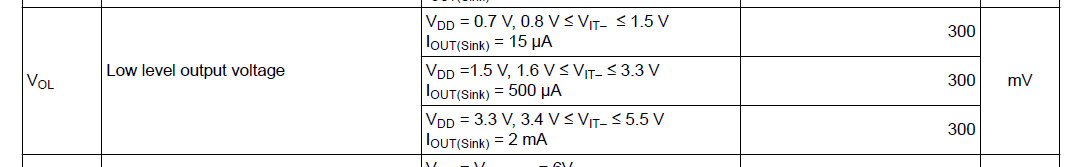

我对 TLV840的 V_OL 规格有疑问。

通常、复位 IC 必须在所有 VDD 范围内保持低电平信号小于 V_IT+/-。

例如、当使用 Vth=2.8V 时、它必须将低电平输出保持在大约0V 至2.8V 之间(我知道它实际上具有 V_POR)。

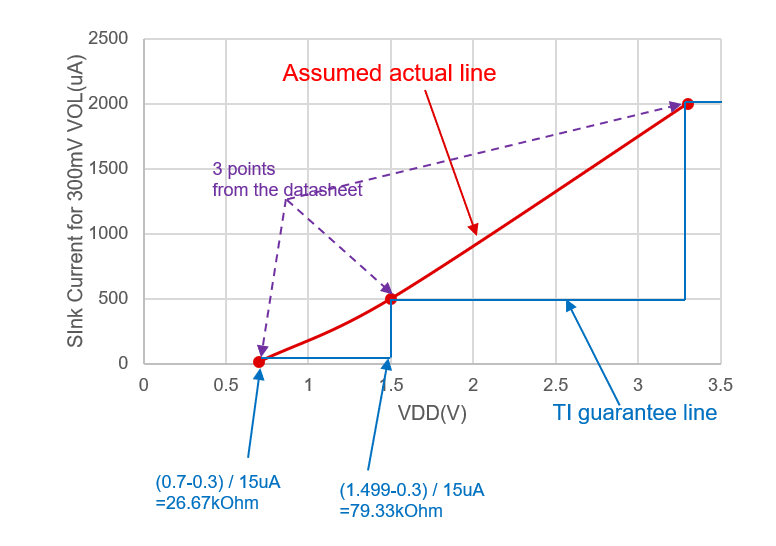

因此、从该规格表中、为了使 VOL 在所有0 ~ 2.8V 范围内保持在300mV 以下、我认为从该表中可以看到 I_OUT (SINK)必须小于15us。

因此我不认为 VDD=1.5V 情况和 VDD=3.3V Canse 没有太多意义。

例如、对于 Vth=3.4V 的器件、使用10K Ω 的上拉电阻、灌电流为

当 VDD =3.3V 时、3.3V/10KOhm = 330uA < 2mA。 没关系。

当 VDD = 3.29V、3.29V/10K Ω= 329uA < 500uA 时、没关系。

当 VDD = 1.49V、1.49V/10Kohm = 149uA > 15uA 时、不正常。 此规格表中的复位输出可能超过300mV。

从这个想法来看、如果用户希望在0V 至 Vth 范围内保持在300mV 以下、他们必须在0.7V 至1.499V 范围内的15uA 条件下使用。

我的理解是否正确?

我觉得这个规格有点奇怪。

此致、

OBA