主题中讨论的其他器件: SN6501

您好专家、

在客户设计中、降压的输入电压为80V、输出电压为60V。 但是、启动时 Vout 上存在30V 预偏置。 该偏置会导致 VHB 至 VHS 差分电压低于指定阈值、UCC27211进入 UVLO。 您是否有任何建议可帮助您启动 UCC27211的偏置电源?

此外、客户还想在 VHB 和 VHS 之间添加12V 隔离式浮动电源。 UCC27211不会使用此隔离式电源进入 UVLO。 您认为这种方法有任何风险吗? 谢谢。

此致、

丹东

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好专家、

在客户设计中、降压的输入电压为80V、输出电压为60V。 但是、启动时 Vout 上存在30V 预偏置。 该偏置会导致 VHB 至 VHS 差分电压低于指定阈值、UCC27211进入 UVLO。 您是否有任何建议可帮助您启动 UCC27211的偏置电源?

此外、客户还想在 VHB 和 VHS 之间添加12V 隔离式浮动电源。 UCC27211不会使用此隔离式电源进入 UVLO。 您认为这种方法有任何风险吗? 谢谢。

此致、

丹东

您好、 Jiandong、

感谢您为客户提供 UCC27211支持。 在您提到的条件下、当 LO 未切换时、HB-HS 偏置将没有充电路径来保持 HB 充电。 当 PWM 脉冲开始时、可能会错过第一个 HO 输出、但当 LO 开关且开关节点转换为接地时、HB 电容器将在该点充电。 如果 LO 脉冲可以放在第一位置、则有助于为 HB 电容器充电。

浮点偏置是一种可以解决此问题的解决方案。 SN6501是一款适用于浮动高侧偏置的出色解决方案。 我建议驱动器的 VDD 在启动序列上的 HB 偏置之前或同时启动。

您好、 Jiandong、

只要 VDD 电压高于 UVLO 阈值、UCC27211 LO 输出就会切换。 如果 VDD 高于 UVLO、即使 HB-HS 偏置低于 HB UVLO、LO 也可以切换。 在许多情况下、典型的启动序列从 VDD 过 UVLO 启动、HI/LI PWM 启动、HB 通常低于 UVLO、直到 LO 开关且 HS 节点切换到接地、从而允许 HB-HS 电容器充电。

此致、

您好 Richard,

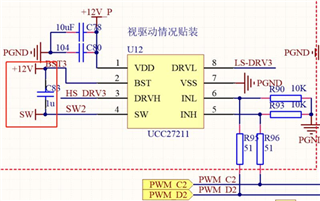

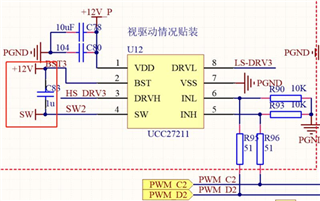

客户发现有关 UCC27211的一些损坏问题、我在随附的 pdf 中描述了此问题。 您能否根据所附的图解和原理图/布局提供一些建议? 谢谢。

此致、

丹东

e2e.ti.com/.../TP_2D00_ZB_2D00_60V120A_2D00_2B1-V1.1_2800_2021.07.02_2900_.PcbDoce2e.ti.com/.../Power.SchDoce2e.ti.com/.../UCC27211-damage-issue.pdf

您好、Jiandong、

我查看了原理图、并在高侧看到一个~80nC Qg FET、并看到一个1uF 的自举电容器。 我看到 HB 电源有浮动偏置、但要快速对 HB 偏置充电、建议尝试使用较小的自举电容值、只要 HB p-p 纹波来自偏置电源。 220nF tp 330nF 的 HB 电容足以驱动具有 HB 偏置低压降的80nC Qg。

一个观察结果是、在 MOSFET 漏极到栅极米勒电荷的开关事件期间、可能会有 Vgs 引起的尖峰。 如果 Vgs 感应电压足够高、则可能会导致击穿。 作为实验、您能否尝试直接在 MOSFET 栅极和源极上添加一些电容、以限制米勒电荷对 Vgs 电压的扰动。

此致、

Herring、您好!

感谢您的回复。

1.客户使用100nF HB 电容器、但没有改进。

2.客户在 MOSFET 栅极和源极上使用了10nF 电容器、但也没有改进。

从我上次答复中连接的波形来看、高侧 MOSFET Vgs 的下降似乎是由 SW 振铃引起的。 当客户在栅极上添加磁珠或增加栅极电阻器时、该压降会得到改善。 根据布局、由于需要大电流、SW 面积非常大。 客户认为 SW 环耦合到 Vgs 的噪声会导致这种压降、您认为这是合理的吗? 您认为是否有任何方法可以证明该噪声是来自 SW 振铃的耦合? 如果您除了更改布局之外还有任何解决方案、这是完美的。

期待您的回复。

此致、谢谢。

丹东

您好、Jiandong、

感谢您的更新以及有关电路板布局问题的其他信息。 我对 MOSFET 栅极和源极上的电容没有作用感到有点惊讶。 但这是一个良好的输入、增加栅极电阻显示出了一些优势。

开关节点上较大的覆铜区会导致该节点上产生更大的寄生电容、从而可能耦合到接地或其他靠近的接近迹线。 为了避免电路板布局变化、我想我会尝试组合一些东西、例如增加一些栅极电阻(或磁珠)以及增加栅源极上的电容。 确保 HB 电容可以支持增加的栅源极电容。 例如、如果添加10nF、则将 HB-HS 电容增加100nF。 确保添加的电容正好位于 MOSFET 栅极和源极引脚上。

否则、减小开关节点平面面积以及接近接地和其他布线将减小开关节点寄生电容和耦合。

此致、

您好 Richard、

感谢您的建议。 下面是一些其他问题:

1、输入电压为80V、标称输出电流为60A、您认为根据经验、SW 上升沿的压摆率适合此应用吗?

2. 客户使用1个 UCC27211驱动2个并联 MOSFET (Qg=80nC)、您认为 UCC27211的4A 峰值拉电流是否足够?

3.为了短接 PCB 的栅极驱动迹线、客户现在更倾向于使用2个 UCC27211 (两个 UCC27211的输入相同)来驱动并联 MOSFET、并且仍然使用单个 L/C 滤波器。 我注意到、每个单元的延迟可能会有很大差异、最大值和最小值差高达30ns。 恐怕这会导致2个并联 MOSFET 无法同时导通或关断。 你有什么建议吗?

4.根据当前情况,您认为是否有比 UCC27211更好的选择,例如,隔离式驱动器如何? 谢谢。

此致

丹东。

您好、Jiandong、

当输入电压为80V、输出电流为60A 时、我看到的电压略高于许多可能介于36V 至75V 之间的输入电压、但增幅不大。 由于额定电压为50V/ns、SW 节点压摆率通常就足够了、如果仅限于驱动器额定值、则 HS 开关时间必须~2ns 才能达到 dV/dt 额定值。

对于估算开关时间、如果假设80nC 在10V 时有效电容为~8nF、则 Vgs 上升时间将为 CDV/I 对于4A、如果您假设转换期间的平均电流为~1/2 4A、则该值为20ns、该值为40ns。 根据开关频率、我认为这是可以的。

对于并联使用两个驱动器的想法、我们尚未在并联驱动器配置中测试半桥驱动器、并且存在驱动器与驱动器时序差异的问题、尤其是在高侧浮动驱动器上。 我建议使用 BJT NPN/PNP 缓冲器来增加更多电流驱动。

我认为有具有更高电流驱动的隔离式驱动器、但我认为单通道驱动器中具有更高的驱动电流、因此成本将明显更高。

此致、