您好!

UCC28070被视为三相全波整流 PFC 的电路。

我知道 UCC28070不支持直流输入、因为

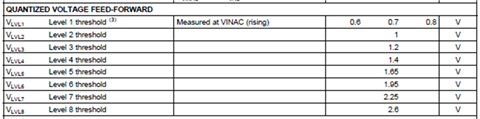

IC 需要使用 VINAC 输入设置正确的乘法器电平。

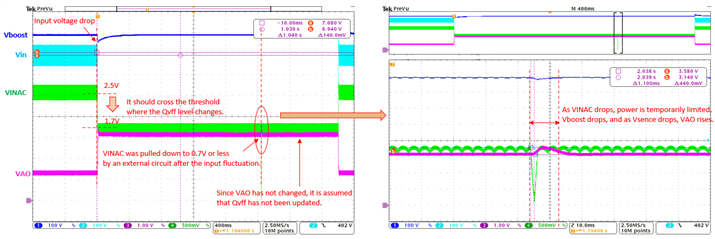

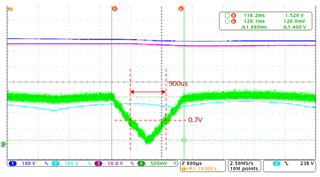

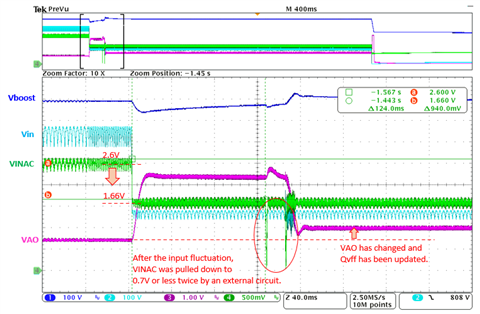

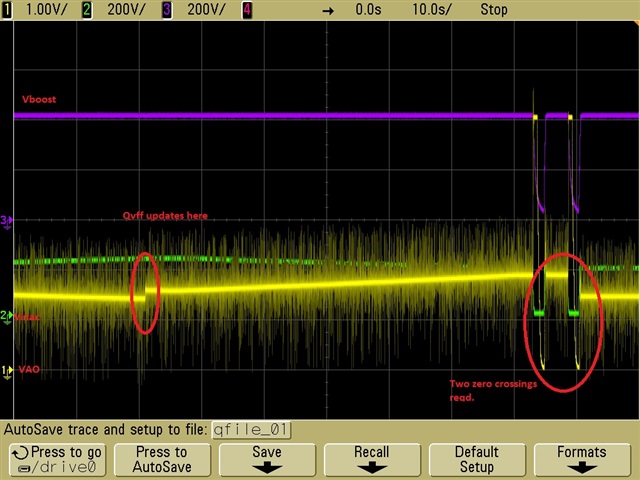

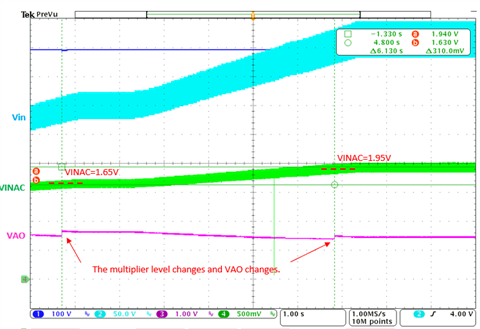

但是、如下面的波形所示、我们已确认当 VINAC 始终高于0.7V 时、乘法器电平会发生变化。

CH2_Vin、CH3_VINAC、CH4_VAO

当 VINAC 超过1.65V 和1.95V 等阈值时、会发生 VAO 变化。 只有当 VINAC 从一个低值过大时、当从一个高值变为一个低值时、VAO 没有变化。

我有以下问题。

VINAC 是否必须降至0.7V 以下才能更新乘法器设置?

是否可以更新乘法器设置而不像上面的波形那样使 VINAC 降至0.7V 以下?

如果发生这种情况、请告诉我控制序列。

以下问题假设可以通过将 VINAC 降至0.7V 以下来更新乘法器设置。

是否可以通过将 VINAC 输入从外部降至0.7V 以下来设置正确的乘法器电平?

当 VINAC 降至0.7V 以下时、使用什么时序输入信息来更新设置?

例如、低于0.7V 之前大约2秒的信息。

此致。